Po K-202

Elżbieta Jezierska-Ziemkiewicz, Andrzej Ziemkiewicz

MERA-400 (1973-1984)

Założenia na minikomputer

- produkowany całkowicie w kraju z dostępnej bazy elementów

- przenośność oprogramowania z systemu K-202

- efektywna wielodostępność

- wieloprogramowość

- wysoka niezawodność systemu

- odporność na zaniki zasilania

- szeroki zakres temperatur pracy

- obsługujący dostępne w kraju urządzenia peryferyjne i pamięci operacyjne

- uwzględniający niektóre standardy systemu SM (np. wymiary płytek drukowanych).

Charakterystyka systemu

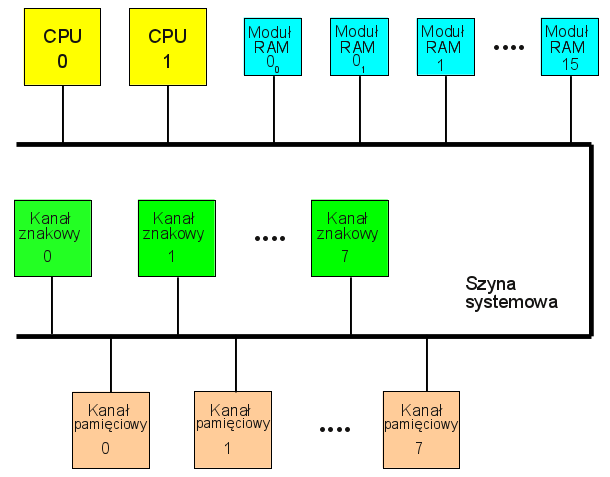

Moduły dołączone były do głównej Szyny Systemu (Interface):

- procesory (do 2),

- pamięci operacyjnej (maksymalnie 17 modułów o pojemności do 64K słów każdy),

- kanały urządzeń zewnętrznych (do 16 kanałów maksymalnie)

Szyna Systemu była asynchroniczna i przesyłała w jednym cyklu:

- dane (16 bitów),

- adresy (20 bitów),

- informacje sterujące.

Priorytet dostępu do Szyny Systemu ustalany był przez układ rozproszony, zrealizowany w postaci ciągu semaforów (patent Andrzeja Karczmarewicza i Elżbiety Jezierskiej-Ziemkiewicz).

Wielodostęp i wieloprogramowość

Przełączanie kontekstu

Istniały dwa stany procesora:

- systemowy,

- użytkowy.

W stanie systemowym wszystkie instrukcje mogły być wykonywane. W stanie użytkowym instrukcje zmieniające stan zasobów systemu były nielegalne. Procesor wchodził w stan systemu w wyniku obsługi przerwania lub wykonania specjalnych instrukcji wołania systemu.

Wprowadzono stos i zdefiniowano wektor stanu procesu. Wektor stanu procesu zawierał:

- Licznik Rozkazów,

- Rejestr Stanu procesu

- ewentualnie rejestry procesora.

Operacje/instrukcje automatycznego przełączania kontekstu wykonywane były w momencie przełączania procesów, wołania podprogramu lub wykonywania przerwania.

Przerwania

Układ przerwań posiadał:

- 32 bitowy rejestr zgłoszeń przerwań

- 10-bitowy rejestr masek przerwań.

Przerwania były obsługiwane według 11 poziomów priorytetowych. Przerwania typu zanik zasilania, błąd i brak pamięci posiadały najwyższy priorytet i nie były maskowane. Procesory pracujące na wspólnej szynie mogły się komunikować wysyłając do siebie dwa rodzaje przerwań o różnych priorytetach.

Pracę w czasie rzeczywistym umożliwiał 32 bitowy rejestr zegara, zliczający impulsy o częstotliwości ustawianej programowo i generujący przerwanie

Lista rozkazów

Zawierała 132 rozkazów i przetwarzała:

- informacje logiczne i arytmetyczne stałoprzecinkowe 16 bitowe,

- informacje arytmetyczne o podwójnej precyzji 32 bitowe,

- informacje zmiennoprzecinkowe 48 bitowe,

- informacje na ciągach znaków.

Rozszerzana była przez programowo wywoływane ekstrakody (do 256). Dostęp do argumentu efektywnego instrukcji mógł być bezpośredni, pośredni lub indeksowany. Te możliwości pozwalały na sprawne manipulowanie złożonymi strukturami danych.

Pamięć operacyjna

Moduł pamięci stanowił zbiór stron. Pojemność strony wynosiła 4K słów. W module mogło być do 16 stron. Każda strona posiadała 8 bitowy identyfikator fizyczny: numer modułu (4 bity) i numer strony (4 bity). Specjalna instrukcja odwołując się do dowolnej strony pamięci przypisywała jej 8 bitowy identyfikator adresu logicznego: 4 bity numeru bloku logicznego i 4 bity numeru strony będące najbardziej znaczącymi bitami adresu logicznego. Dane te były umieszczane w pamięci asocjacyjnej znajdującej się w każdym module pamięci. Po starcie systemu tylko 12K słów bloku systemowego o numerze 0 było aktywne. Reszta pamięci była nieaktywna i nie odpowiadała na polecenia odczytu i zapisu.

Adresacja pamięci była dwuwymiarowa:

- numer bloku logicznego (4 bity)

- numer logiczny strony (4 bity).

Dostęp do pamięci z procesorów i z kanałów wejścia/wyjścia odbywał się z użyciem adresu logicznego. W danym momencie w systemie mogło być aktywnych do 15 użytkowych bloków logicznych i jeden blok systemowy w każdym procesorze.

Bloki logiczne pamięci były tworzone dynamicznie przez system operacyjny, który uruchamiając proces przydzielał mu pamięć. Dopiero po wykonaniu tego przyporządkowania strona pamięci stawała się aktywna i odpowiadała na polecenia odczytu i zapisu. Bloki logiczne pamięci mogły być tworzone z dowolnych stron, nawet znajdujących się w różnych modułach pamięci.

Własność ta była niezwykle ważna. W innych systemach pamięć operacyjna rozpoznaje jedynie swój adres fizyczny, więc wymaga to translacji adresów logicznych na adresy fizyczne. Stwarza to niebezpieczeństwo uszkodzenia pamięci innych procesów. Wirtualny mechanizm programowego i dynamicznego przydziału pamięci do procesu w Mera-400 zapewniał pełną ochronę pamięci w pracy wieloprocesowej (wieloprogramowej). Innymi możliwościami tego rozwiązania były: możliwość użycia programów reentrent, dzielonych przez wiele procesów bez konieczności tworzenia wielu kopii oraz możliwość przekazywania danych z jednego procesu do innego poprzez dynamiczne przełączanie stron pomiędzy procesami.

Do konstrukcji pamięci operacyjnej stosowane były rożne nośniki: początkowo były to pamięci ferrytowe o rożnym czasie cyklu, następnie pamięci na cienkich warstwach magnetycznych, a również pamięci drutowe. Po roku 1984 opracowana została pamięć operacyjna na układach scalonych półprzewodnikowej pamięci typu DRAM.

Kanały wejścia-wyjścia

W systemie mogło być dołączonych do 16 kanałów różnego typu: kanały znakowe, kanały pamięciowe oraz kanały automatyki. Inicjowanie transmisji mogło być wykonane również z poziomu programu użytkowego. Pozwalało to użytkownikom dołączać i oprogramowywać swoje prywatne sterowniki.

Do kanałów typu znakowego miedzy innymi opracowane były jednostki sterujące następujących urządzeń znakowych:

- czytniki taśmy papierowej CT1001A, CT2100,

- perforatory taśmy DT105s, FACIT 4070,

- drukarka mozaikowa DZM180,

- drukarka wierszowa DW3,

- monitory ekranowe Videoton, ALFA311,

- grafoskop MMG300,

- dowolne urządzenia pracujące w standardzie V24 (np. modemy telefoniczne),

- pisak x-y typu DIGIGRAF 1008.

Do kanałów pamięciowych pracujących z dostępem DMA można było dołączać do 8 urządzeń pamięciowych. Opracowano miedzy innymi następujące kontrolery:

- pamięci dyskowej MERA 9425,

- pamięci taśmowych PT305,

- pamięci kasetowej PK1,

- pamięci na miękkim dysku LX45.

Konstrukcja mechaniczna

Pakiety procesora, pamięci operacyjnej i kanałów wejścia/wyjścia miały wymiary 295x300 mm. Pakiety jednostek sterujących urządzeniami peryferyjnymi były pół-pakietami o wymiarach 140x300mm. Wyprodukowano około 650 systemów MERA-400 początkowo w ZDM IMM, a następnie w OBR ERA. Po roku 1976 pracami nad rozwojem i produkcją MERY-400 kierował Jerzy Dżoga. Instytut MERA-PIAP opracował kanały automatyki systemu PI i CAMAC.

Zespół

Hardware

Główny Konstruktor: Elżbieta Jezierska-Ziemkiewicz

- Jednostka Centralna, Zmienny Przecinek, Pamięć Operacyjna: Elżbieta Jezierska-Ziemkiewicz, Henryk Wojtowicz, Jeremi Witewski

- Kontrolery pamięci dyskowej i taśmowej: Jerzy Zajdel, Anna Srebrna, Jerzy Dyczkowski, Joanna Kowalczyk, Z. Kopczyńska

- Kontrolery urządzeń znakowych: Jerzy Zawisza, Krzysztof Szaniawski, A. Chrząszcz

Software

Główny Programista Teresa Pajkowska

- Systemy Operacyjne:

- SOM 1: ZDM IMM: Leszek Grzyb, Andrzej Mozgawa

- SOM 3: ZDM IMM: Wojciech Szanser, Michał Skolimowski

- SOM 5: PIAP: Stanisław Chrobot

- CROOK: PG (Koordynację prac i dystrybucję systemu z ramienia IMM prowadził Andrzej Ziemkiewicz): Zbigniew Czerniak, Marek Nikodemski, Włodzimierz J. Martin

- SOM 7: II UW: Piotr Findeisen, Paweł Gburzyński

- Języki programowania

- C: Politechnika Gdańska

- BASIC: Politechnika Gdańska

- Fortran, CSL, LISP, ALGOL, MODULA-2: Politechnika Poznańska: Janusz Gocałek

- LOGLAN Uniwersytet Warszawski: Andrzej Salwicki

- Cross-kompilator i symulator procesora Intel 8080/8085: ZDO IMM: Andrzej Ziemkiewicz i Andrzej Karczmarewicz

- System graficzny przewidziany do CAD z użyciem monitora wektorowego: ZDO IMM: Andrzej Ziemkiewicz i Andrzej Karczmarewicz

- System pomiarowy z użyciem interface'u IEEE: ZDM IMM: Andrzej Ziemkiewicz, Tadeusz Wilczek i Bożena Padzik,

MX16 - AMEPOL (1984-1988)

Charakterystyka systemu

W 1984 roku ERA zakończyła produkcję MERY-400. Wówczas w firmie polonijnej AMEPOL utworzył się zespół na bazie "starej ekipy" MERA-400 i nowych ambitnych osób. W nowej ulepszonej konstrukcji mechanicznej umieszczony został procesor MERA-400 oraz nowo opracowane moduły systemu: moduł półprzewodnikowej pamięci operacyjnej i procesory peryferyjne. Moduł pamięci operacyjnej był pamięcią półprzewodnikową zbudowaną na elementach DRAM. Nowe procesory peryferyjne mogły zastąpić stare kanały wejścia/wyjścia.. Ich konstrukcja bazowała na mikroprocesorach INTEL 8085. Jako sterowniki urządzeń peryferyjnych wykorzystywano dostępne wówczas scalone kontrolery INTEL lub ich klony. Były to:

- MULTIX – procesor multipleksorowy z możliwością dołączania do 256 urządzeń zewnętrznych i prowadzący równoczesna transmisję z wielu urządzeń do niego dołączonych

- PLIX - procesor selektorowy z jedną transmisją aktywną w danym momencie, poprzez który pracowały dyski typu Winchester, pamięci taśmowe itp,

- IEC - procesor pomiarowy. Procesor ten wyposażony był w dwu-wejściową pamięć, która była częścią kanału i równocześnie była dołączona do szyny głównej systemu, jak normalny moduł pamięci operacyjnej. W zamierzeniu było wykorzystanie go do sterowania urządzeniami pomiarowymi z interface'em IEC, a w szczególności aparatury medycznej. W dalszej perspektywie było dołączanie aparatury graficznej i innych urządzeń wymagających przesyłanie dużych zbiorów informacji.

Zespół

Przy opracowaniu i produkcji MX16 pracował zespół w składzie:

- Elżbieta Jezierska-Ziemkiewicz,

- Jerzy Dżoga,

- Andrzej Karczmarewicz,

- Andrzej Ziemkiewicz,

- Tadeusz Wilczek,

- Stanisław Chmielewski,

- Dariusz Cielebąk,

- Bożena Marchewka-Padzik,

- Włodzimierz Bielski,

- Inka Pyziak,

- i wielu innych osób, które przepraszam, ze nie umieściłam na liście.

Wyprodukowano około 30 egzemplarzy systemu MX16 oraz rozbudowano o nowe moduły istniejące zestawy MERA 400 wyprodukowane w Zakładach Systemów Minikomputerowych ERA.

SOLID (grudzień 1980 - grudzień 1981)

W grudniu 1980 roku Naczelny Dyrektor Zjednoczenia MERA dr inż Zdzisław Łapiński powołał zespól do opracowania komputera będącego następcą MERA 400 (Aneks). W skład zespołu powołano osoby z:

- IMM,

- OBRTKiP,

- PSK MERA-SYSTEM.

Współpracowali pracownicy z:

- UW,

- Politechniki Gdańskiej,

- Politechniki Poznańskiej,

- oraz specjaliści od układów scalonych z CEMA.

Ramowa koncepcja komputera zwanego SOLID została przedstawiona na konferencji, która odbyła się w IMM 7 grudnia 1981 roku. Po 13 grudnia 1981 roku wszelki ślad tych prac zaginał.