Zegar czasu rzeczywistego Amepolu

Opis funkcjonalny

Zegar czasu rzeczywistego z loaderem systemu opracowany dla maszyny cyfrowej MERA-400 ma za zadanie usprawnienie czynności operatorskich podczas uruchamiania systemu. Układ składa się z dwóch części:

- z części zegarowej, która ma za zadanie odliczanie czasu i umożliwienie odczytania bieżącego czasu i daty przez procesor,

- z części dotyczącej przechowywania loadera systemu w pamięci PROM i jego odczytu do pamięci operacyjnej przez procesor.

Obie te części korzystają ze wspólnego dekodera rozkazów, który umożliwia, na podstawie kodu operacji, selektywną współpracę procesora z jednym lub drugim układem. Układ pracuje w kanale znakowym minikomputera, w miejscu przeznaczonym dla jednostek sterujących urządzeń znakowych, na dowolnej z ośmiu pozycji, która określa jego numer.

Operacje wykonywane przez układ zegar + loader

Procesor współpracuje z opisywanym układem przy pomocy rozkazu IN, wykonującego operację pobrania informacji z urządzenia. Argument efektywny rozkazu niesie informację określającą:

| Bity argumentu | Znaczenie |

|---|---|

| 0-5 | kod operacji |

| 6 | kod niewykorzystany |

| 7 | - |

| 8-10 | numer urządzenia w kanale znakowym |

| 11-14 | numer kanału znakowego |

| 15 | = 0 (bit określający rozkaz wysłany do kanału) |

Zależnie od kodu operacji zawartego na bitach 0-6 urządzenie może wykonywać operacje przedstawione w tabeli:

| Kod operacji | Treść operacji | Odpowiedź |

|---|---|---|

| 1xxxxx | Czytaj znak z pamięci PROM zawierającej loader systemu. R)A)8-15 := ZNAK |

OK |

| 01xxxx | Ustaw bit HS w rejestrze trybu pracy zegara. R)A)0-15 := STAN ZEGARA |

OK |

| 00xxxx | Zeruj bit HS. R)A)0-15 := STAN ZEGARA |

OK |

| 0x1xxx | Ustaw bit MS w rejestrze trybu pracy zegara. R)A)0-15 := STAN ZEGARA |

OK |

| 0x0xxx | Zeruj bit MS. R)A)0-15 := STAN ZEGARA |

OK |

| 0xx0xx | Ustaw bit DR w rejestrze trybu pracy zegara. R)A)0-15 := STAN ZEGARA |

OK |

| 0xx1xx | Zeruj bit DR. R)A)0-15 := STAN ZEGARA |

OK |

| 0xxx0x | Ustaw bit TR w rejestrze trybu pracy zegara. R)A)0-15 := STAN ZEGARA |

OK |

| 0xxxx1 | Odblokuj przerwania zegarowe. R)A)0-15 := STAN ZEGARA |

OK |

| 0xxxx0 | Zablokuj przerwania zegarowe. R)A)0-15 := STAN ZEGARA |

OK |

Poszczególne operacje dotyczące zegara (bit N0=0) można sumować przez ustawienie odpowiednich bitów N1-N5. Urządzenie zgłasza do procesora przerwania zegarowe po uprzednim ich odblokowaniu. Specyfikacja tego przerwania podawana na szyny P-DTIN 5-7 ma wartość 0.

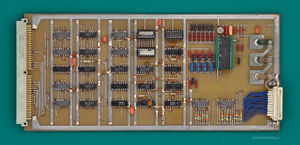

Budowa i działanie układu zegara z loaderem

Styk urządzenia z kanałem znakowym

Wykorzystywane są następujące sygnały interface'u znakowego:

- P-Fi - strob operacji pobrania

- P-OK - potwierdzenie wykonania operacji

- P-AD0-5 - kod operacji

- P-DTIN0-15 - informacja urządzenia

- P-IN - zgłoszenie przerwania

- P-PSPi - żądanie specyfikacji przerwania

- P-CL - zerowanie ogólne

Indeks "i" związany jest z numerem fizycznym urządzenia zależnym od miejsca zajmowanego w kanale.

Operacje wykonywane przez urządzenie

Urządzenie odbiera z kanału znakowego strob -P-F oraz sygnały -P-AD0-5 zawierające kod operacji i może wykonać następujące operacje pobrania (w nawiasach podano kod operacji odpowiadający bitom -P-AD0-5, "x" oznacza dowolną wartość bitu).

- (1xxxxx) - czytaj znak z pamięci PROM zawierającej loader systemu. Po każdym pobraniu licznik adresu zwiększany jest o 1. Zerowanie licznika adresu realizowane jest sygnałem zerowania ogólnego lub w wyniku przepełnienia po odczytaniu ostatniego znaku zapisanego w pamięci. Każda operacja kwitowana jest odpowiedzią OK.

- (01xxxx) - ustaw bit HS (nastawianie godzin) w rejestrze trybu racy zegara. Ustawienie tego bitu powoduje wysterowanie wejścia HS zegara i wykonywanie operacji HS. Operacja ta realizowana jest tak długo jak długo bit HS w rejestrze trybu pracy zegara jest ustawiony, czyli do momentu wykonania operacji zeruj bit HS.

- (00xxxx) - zeruj bit HS. Powoduje wyzerowanie bitu HS i tym samym zakończenie wykonywania przez zegar operacji HS.

- (0x1xxx) - ustaw bit MS (nastawianie minut). Działanie identyczne jak dla operacji "ustaw bit HS".

- (0x0xxx) - zeruj bit MS.

- (0xx0xx) - ustaw bit DR (odczyt daty).

- (0xx1xx) - zeruj bit DR.

- (0xxx0x) - ustaw bit TR (odczyt czasu).

- (0xxx1x) - zeruj bit TR.

- (0xxxx1) - odblokuj przerwania zegarowe. Przerwania generowane są co 0,5 s.

- (0xxxx0) - zablokuj przerwania zegarowe.

Poszczególne operacje dotyczące zegara mogą być wykonywane łącznie, przez ustawienie lub wyzerowanie odpowiednich bitów kodu operacji. Sposób pracy zegara przy uaktualnieniu odpowiednich wejść sterujących pokazuje tabela.

| Rodzaj pracy zegara | Uaktywnione wejścia sterujące |

Czas wyświetlania inf. od momentu uaktywnienia wejść sterujących | |

|---|---|---|---|

| Pokazywanie | Nastawianie | ||

| godzin, minut | - | w sposób ciągły | |

| sekund | TR | po 1,25s pokazywane na przemian z godziną i minutami z częstotliwością 1Hz | |

| miesiąca, dnia | DR lub TR, DR | przez 1,25s | |

| godzin | HS lub HS, TR | czasowi uaktywnienia | |

| minut | MS lub MS, DR | czasowi uaktywnienia | |

| godzin i minut | MS, HS lub MS, HS, DR | czasowi uaktywnienia | |

| miesięcy | HS, DR | czasowi uaktywnienia | |

| dni | HS, TR, DR | czasowi uaktywnienia | |

Po włączeniu zasilania lub po ustawieniu minut, sekundy zą zerowane i liczenie zostaje wznowione po uaktywnieniu wejścia TR. Nie zaleca się stosowania następujących kombinacji operacji: (MS, TR), (MS, TR, DR), (MS, HS, TR) oraz (MS, HS, TR, DR) gdyż w tych przypadkach przy nastawieniu minut nie jest wstrzymywane liczenie sekund.

Przerwania

Układ zgłasza do procesora przerwania zegaowe po ich odblokowaniu operacją "odblokuj przerwania". Przerwania są zgłaszane co 0,5s. Specyfikacja tych przerwań podawana na szyny -P-DTIN 5-7 jest równa (000). Przerwania wykorzystywane są przez system operacyjny i określają momenty generowania operacji dotyczących zegara.

Dekoder rozkazów

Strob operacji pobrania -P-F po ziloczynowaniu z sygnałem -D-AD0 i jego negacją na bramkach E3-3 i E3-11 tworzy sygnały FAD0 i ~FAD0. Dodatkowo po małym opóźnieniu zrealizowanym na elementach R15, C5 generowany jest sygnał odpowiedzi -P-OK. Każda operacja pobrania skierowana do pakietu zegara kwitowana jest odpowiedzią OK.

Rejestr operacji i układ przerwań

Sygnałem FAD0 generowanym przez dekoder rozkazów wpisywany jest do rejestru operacji stan linii AD1-AD5. Rejestr operacji zbudowany jest z czterobitowego rejestru F4 oraz przerzutnika F3-8. Stan linii P-AD1 i P-AD2 oraz zanegowanych P-AD3 i P-AD4 po wpisaniu do rejestru steruje poprzez bramki F5 typu OC wejścia sterujące trybem pracy zegara. Stan linii -AD5 wpisywany do przerzutnika F3-8 zezwala lub nie na zgłaszanie przerwań, poprzez wejścia ustawiające przerzutnika F3-5. Jeśli wejście to jest w stanie "0", na wyjściu przerzutnika zostaje wymuszony stan "1" i zegar nie zgłasza przerwań. Jeśli wejście to jest w stanie "1", impuls z wyjścia zegara oznaczonego "2Hz" powoduje zmianę stanu przerzutnika i zgłoszenie przerwania po linii -P-IN. Sygnał P-PSP poprzez bramkę E3-6 przywraca poprzedni stan przerzutnika co powoduje zdjęcie przerwania. Cykl taki powtarzany jest do momentu pojawienia się "0" na wyjściu F3-8. Powoduje to poprzez bramkę E3-6 zablokowanie przerzutnika zgłaszania przerwań, który nie reaguje na impulsy "2Hz" podawane na wejście zegarowe.

Sygnał P-CL powoduje wyzerowanie rejestru operacji i tym samym zablokowanie przerwań. Stan linii P-AD3, P-AD4 jest negowany przed wpisaniem do rejestru operacji ponieważ operacje o kodzie = 0 są wychwytywane przez kanał znakowy jako adresowane do niego. Negacja tych dwu linii wymusza niezerowy kod operacji dla wszystkich wykorzystywanych kombinacji sygnałów sterujących pracą zegara.

Układ zegara

Zegar zrealizowany został w oparciu o układ scalony MC 1204. Zasada pracy tego układu opisana jest w jego aplikacji wydanej przez Instytut Technologii Elektronowej w Warszawie. Układ MC 1204 przystosowany jest do współpracy z 4-cyfrowym wyświetlaczem typu LED z multiplexowanym sposobem wyświetlania informacji.

Sygnały D1-D2 sterujące katodami wyświetlacza zostały wykonane jako sygnały strobujące wpisem kolejnych cyfr daty lub czasu do rejestru typu "zatrzask". Ze względu na małą obciążalność wyjść D1-D4 zastosowano wzmacniacze typu MCY 74049. Sygnały D1-D4 po opóźnieniu zrealizowanym na układach RC i bramce z wejściem Schmidta potrzebnym na ustalenie się sygnałów na wyjściach a-g zegara wyzwalają miniwibratory typu UCY 74123. Impulsy generowane przez te miniwibratory powodują wpisanie do rejestru wyjściowego kolejnych cyfr odczytywanego czasu lub daty. Ponieważ zegar generuje cyfry w kodzie wskaźnika siedmiosegmentowego zastosowano konwerter kodou wskaźnika na kod BCD zrealizowany na pamięci PROM.

Wyjścia połączone są z wejściami rejestru wyjściowego tak by kolejne cyfry wpisywać do jego czterobitowych części. Aby rozróżnić odczyt czasu od odczytu daty na najstarszy bit rejestru wyjściowego wprowadzono wyjście segmentu "+" który steruje w przypadku wskaźnika dwukropkiem oddzielającym cyfry godzin od cyfr minut. Dwukropek jest sterowany jako segment "+" pierwszej cyfry i jest wyświetlany tylko podczas odczytywania czasu. Stan rejestru wyjściowego nadawany jest przez bramki wyjściowe typu UCY 7403 otwierane sygnałem FAD0 na szyny DTIN. Każda operacja dotycząca powoduje więc podniesienie stau rejestru wyjściowego na szyny DTIN. Ponieważ pierwsza cyfra wpisywana do rejestru F2 może przybierać tylko wartości 1 i 2 (zero nieznaczące nie jest wyświetlane) nie wszystkie wejścia rejestru są połączone z odpowiednimi wyjściami konwertera kodu.

Pamięć loadera systemu

Pamięć ta została zrealizowana na dwóch czterobtowych układach pamięci typu PROM tworząc ośmiobitową strukturę. Treść programu zostaje na stałe zapisana w tej pamięci w fazie programowania.

Rejestr adresowy pamięci zrealizowany został na dwóch czterobitowych licznikach typu UCY 7493. Każda operacja pobrania dotycząca pamięci sygnałem FAD0 z dekodera rozkazów powoduje podanie zawartości słowa pamięci określonego przez zawartość rejestru adresowego na szyny DTIN9-15. Po każdej operacji odczytu stan rejestru adresowego zostaje zwiększony o 1. Rejestr jest zerowany sygnałem zerowania ogólnego P-CL lub w wyniku przepełnienia po odczytaniu całej zawartości pamięci. Odczyt pamięci może być tylko sekwencyjny.

Układ sterowania wyświetlaczem (opcja)

Możliwe jest dołączenie do układu zegara wyświetlacza złożonego z 4 wskaźników siedmiosegmentowych typu LED ze wspólną katodą. W tym celu sygnały D1-D4 oraz a-g poprzez wzmacniacze tranzystorowe zostały wyprowadzone na złącze krawędziowe. Możliwe jest także sterowanie zegara zewnętrznymi przełącznikami dołączonymi do [...] F5 sterujących wejścia HS, MS, DR, TR układu zegarowego. Sygnały D1-D4 oraz a-g zostały wyprowadzone na złącze krawędziowe także wprost i mogą być użyte np. w przypadku zastosowania innego wyświetlacza po odpowiednim wzmocnieniu.

Zasilanie

Układ zegara zasilany jest z dwóch źródeł. Po włączeniu komputera i pojawieniu się napięcia +5V zasilającego pakiet, układ jest zasilany z tego napięcia poprzez diodę D1. Ponieważ napięcie to jest wyższe od napięcia akumulatorów (3,6V) dioda D2 odcina zasilanie z akumulatorów. Akumulatory są doładowywane poprzez rezystor R1. Po zaniku napięcia +5V układ zasilany jest z akumulatorów.

Oprogramowanie

Układ zegara należy zdefiniować w tablicy konfiguracji systemu CROOK-4. W komórce o adresie 056 powinien znajdować się systemowy numer urządzenia.

Do ustawiania zegara służy program CLOCK. W 1 komórce programu umieszczany jest adres fizyczny zegara w postaci:

- bity 11-14 - numer kanału,

- bity 8-10 - numer urządzenia.

Ustawianie zegara odbywa się przez wywołanie programu:

CLOCK, (miesiąc), (dzień). (godzina), (minuta) [CR]

program przeprowadza operację ustawienia zegara, wyświetlając na końcówce jej przebieg. Po ustawieniu zegar jest zatrzymany. Aby rozpocząć liczenie należy wywołać program CLOCK bez parametrów:

CLOCK [CR]

Program poda na końcówce aktualny czas i datę, i uruchomi zegar.

Źródło: DTR zegara czasu rzeczywistego do minikomputera MERA-400, Amepol