MULTIX od środka: Różnice pomiędzy wersjami

| (Nie pokazano 81 pośrednich wersji utworzonych przez tego samego użytkownika) | |||

| Linia 3: | Linia 3: | ||

= Sprzęt = | = Sprzęt = | ||

MULTIX to komputer zbudowany w oparciu o procesor Intel 8085 | MULTIX to komputer zbudowany w oparciu o procesor Intel 8085, z programem sterującym (firmware) zapisanym w pamięci ROM. Z punktu widzenia MULTIX-a MERA-400 jest jednym z jego urządzeń zewnętrznych, widzianym przez pryzmat sprzęgu znajdującego się pomiędzy magistralami MERY-400 a MULTIX-a. | ||

Komunikacja MERY-400 z MULTIX-em odbywa się przy użyciu: | |||

* | * jednego z przerwań procesora 8085, które informuje o nadejściu polecenia wysłanego rozkazami IN/OU z MERY-400 | ||

* | * rejestrów sprzętowych sprzęgu przechowujących odczytane z magistrali MERY-400 argumenty polecenia IN/OU | ||

* | |||

* | Komunikacja MULTIX-a z MERĄ-400 odbywa się przy użyciu: | ||

* odczytu/zapisu pamięci MERY-400 (przy użyciu kontrolera DMA) | |||

* zgłoszenia przerwania kanałowego do MERY-400 | |||

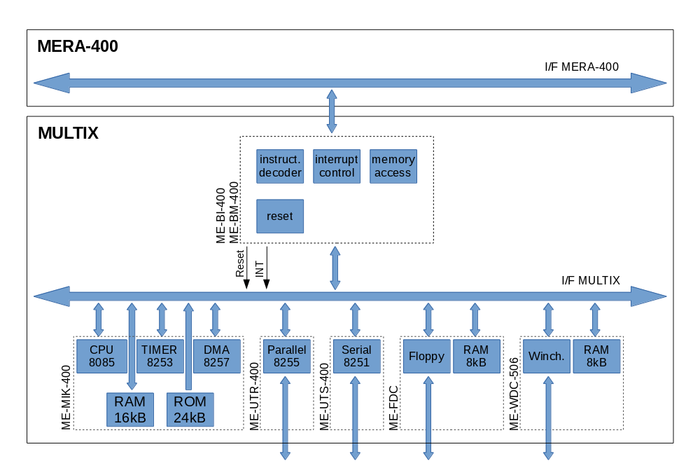

** | Poniższy schemat blokowy przedstawia budowę MULTIX-a (wraz z podziałem na pakiety) i sprzęg z MERĄ-400. | ||

* DMA: | [[File:multix-internals.png|700px|center|Schemat blokowy MULTIX-a]] | ||

== Pakiety == | |||

Bloki funkcjonalne MULTIX-a i kontrolery urządzeń wejścia/wyjścia rozlokowane są na "wąskich" pakietach MERY-400. | |||

=== ME-MIK-400 === | |||

ME-MIK-400 to pakiet mikrokomputera zawierający: | |||

* CPU: 8085 3MHz (NEC D8085AC) | |||

* pamięć EPROM 3x8KB | |||

* pamięć RAM 2x8KB Hitachi HM6264LP-15 | |||

* Timer: 8253 (NEC M5L8253P-5) | |||

* DMA: 8257 (NEC D8257C-2) | |||

** kanał 1: MERA-400 | ** kanał 1: MERA-400 | ||

** kanał 2: taśma | ** kanał 2: taśma | ||

** kanał 3: autoload | ** kanał 3: autoload | ||

* | |||

* | === ME-BI-400 i ME-BM-400 === | ||

ME-BI-400 i ME-BM-400 to pakiety sprzęgu zapewniające komunikację między MULTIX-em a MERĄ-400. Realizują one m.in. następujące funkcje: | |||

* Od strony interfejsu MERY-400: | |||

** dekodowanie i realizację krytycznych rozkazów I/O | |||

** zgłaszanie przerwania kanałowego | |||

** transmisję danych do/z PAO | |||

* Od strony MULTIX-a: | |||

** sprzętowe rejestry I/O | |||

** reset MULTIX-a i urządzeń podległych | |||

** zarządzanie przerwaniem "polecenie sterujące" | |||

=== ME-UTR-400 === | |||

Cztery porty równoległe zrealizowane na dwóch układach 8255 (NEC D8255AC-2). Pakiet występuje w wersjach ME-UTR-1, ME-UTR-2 i ME-UTR-3, pozwalających na podłączenie różnego rodzaju urządzeń równoległych | |||

=== ME-UTS-400 === | |||

Cztery porty szeregowe zrealizowane na czterech układach 8251 (NEC M5L8251AP-5). Pakiet występuje w wersjach ME-UTS-1, ME-UTS-2 i ME-UTS-3, pozwalających na podłączenie urządzeń różnymi interfejsami (V24 lub prądowym z optoizolacją) i dających różne dodatkowe możliwości ich konfiguracji. | |||

=== ME-FDC === | |||

Kontroler czterech stacji dyskietek zrealizowany w oparciu o: | |||

* kontroler Zilog Z0765A08PSC | |||

* DMA 8257 (NEC M5L8257P-5) | |||

* pamięć RAM 8KB Hitachi HM6264LP-15 | |||

=== ME-WDC-506 === | |||

Kontroler czterech dysków ST-506 (winchester) zrealizowany w oparciu o: | |||

* kontroler Intel C82062-00 | |||

* pamięć RAM 8KB Hitachi HM6264LP-15 | |||

= Mapa pamięci = | = Mapa pamięci = | ||

| Linia 27: | Linia 75: | ||

! Adres !! Nazwa !! Zawartość | ! Adres !! Nazwa !! Zawartość | ||

|- | |- | ||

| 0x0000- | | 0x0000-0x1fff || || EPROM 1 | ||

|- | |||

| 0x2000-0x3fff || || EPROM 2 | |||

|- | |- | ||

| 0x6000 || RAM || RAM (16KB | | 0x4000-0x5fff || || EPROM 3 | ||

|- | |||

| 0x6000-0x9fff || RAM || RAM główna (16KB) | |||

|- | |- | ||

| 0x6000+154 || STACK || koniec stosu, początek dostępnej RAM | | 0x6000+154 || STACK || koniec stosu, początek dostępnej RAM | ||

| Linia 38: | Linia 90: | ||

|- | |- | ||

| 0xff00-0xffff || AD || we/wy widziane jako pamięć | | 0xff00-0xffff || AD || we/wy widziane jako pamięć | ||

|} | |||

{| class="wikitable" | |||

! Adres !! Nazwa !! Zawartość | |||

|- | |||

| 0-2 || || JMP IZER | |||

|- | |||

| 3 || || 0 | |||

|- | |||

| 4 || || suma kontrolna ROM | |||

|- | |||

| 5-6 || || ostatni adres ROM | |||

|- | |||

| 7 || || ? | |||

|- | |||

| 8-0x3f || || przerwania 8085 | |||

|- | |||

| 0x4f || BEGPR || początek programu | |||

|- | |||

| 0x6000 || RAM || POCZATEK RAM | |||

|- | |||

| 0x6000-0x6020 || || tablica przerwań (ZAWIERA: JMP <ADRES>) | |||

|- | |||

| 0x6000 || || JMP IKWIT - 1 | |||

|- | |||

| 0x6003 || || JMP IZEGA - 2 | |||

|- | |||

| 0x6006 || || JMP IOPRQ - 3 | |||

|- | |||

| 0x6009 || || JMP INUS4 - 4 | |||

|- | |||

| 0x600c || || JMP ITRAP - 4.5 | |||

|- | |||

| 0x600f || || JMP IWINC - 5 | |||

|- | |||

| 0x6012 || || JMP IPOST - 5.5 | |||

|- | |||

| 0x6015 || || JMP ITAPE - 6 | |||

|- | |||

| 0x6018 || || JMP IKASE - 6.5 | |||

|- | |||

| 0x601b || || JMP IKAPA - 7 | |||

|- | |||

| 0x601e || || JMP IDMA - 7.5 | |||

|- | |||

| 0x6021 || NUPRO || NR PROCESORA DLA <SETKO> | |||

|- | |||

| 0x6022 || STBOT || dno stosu | |||

|- | |||

| 0x609a || STACK = RAM+154 || KONIEC STOSU=POCZATEK DOSTEPNEJ RAM | |||

|- | |||

| 0x609a-0x609b || FINRA || ostatni adres sprawnej RAM | |||

|- | |||

| 0x609c || RAM00 || początek pamięci zerowanej | |||

|- | |||

| 0x60a3-0x60a4 || RAMUS || adres wykorzystanej ram +1 | |||

|} | |} | ||

== I/O == | == I/O == | ||

Rejestry I/O z punktu widzenia MULTIX-a mogą być używane do: | |||

* odczytu lub zapisu (R, W) | |||

* tylko odczytu (R) | |||

* sterowania (S) | |||

Operacje odczytu i zapisu są intuicyjne, natomiast sterowanie ma następujący przebieg: | |||

# MULTIX wykonuje operację odczytu (IN) na rejestrze | |||

# Sprzęg MULTIX-MERA wykonuje operację właściwą dla funkcji rejestru (np. zgłasza przerwanie do procesora) | |||

# W akumulatorze zwracany jest rezultat wykonanej przez sprzęg operacji (wartość różna w zależności od rejestru, oznaczająca np.: OK, błąd parzystości, etc.) | |||

{| class="wikitable" | {| class="wikitable" | ||

! Adres !! R/W !! Nazwa !! Znaczenie | ! Adres !! R/W/S !! Nazwa !! Znaczenie | ||

|- | |||

| align="center" bgcolor="Cornsilk" colspan="4" | <b>MERA-400</b> | |||

|- | |- | ||

| 0-1 || R || DANEI || dane odczytane z MERA-400 (MSB, LSB) | | 0-1 || R || DANEI || dane odczytane z MERA-400 (MSB, LSB) | ||

| Linia 65: | Linia 187: | ||

| 7 || W || SPECI+1 || specyfikacja przerwania: numer linii | | 7 || W || SPECI+1 || specyfikacja przerwania: numer linii | ||

|- | |- | ||

| 8 || | | 8 || S || KOTRA || Rozkaz "koniec transmisji" | ||

|- | |- | ||

| 10 || | | 10 || S || PISZB || Rozkaz "pisz blok przez DMA do MERA-400" | ||

|- | |- | ||

| 11 || | | 11 || S || CZYTB || Rozkaz "czytaj blok przez DMA z MERA-400" | ||

|- | |- | ||

| 12 || | | 12 || S || PISZP || Rozkaz "pisz do MERA-400" | ||

|- | |- | ||

| 13 || | | 13 || S || CZYTP || Rozkaz "czytaj z MERA-400" | ||

|- | |- | ||

| 14 || | | 14 || S || INTR0 || Rozkaz "zgłoś przerwanie do MERA-400" (procesor 0) | ||

|- | |- | ||

| 15 || | | 15 || S || INTR1 || Rozkaz "zgłoś przerwanie do MERA-400" (procesor 1) | ||

|- | |- | ||

| 0x38 || W || KOPRQ || pokwitowanie OPRQ | | 0x38 || W || KOPRQ || pokwitowanie OPRQ | ||

|- | |- | ||

| 0x4e || W || WUUPG || ustawienie maski przerwań 'INTR' | | 0x4e || W || WUUPG || ustawienie maski przerwań 'INTR' | ||

|- | |||

| align="center" bgcolor="Cornsilk" colspan="4" | <b>Timer</b> | |||

|- | |- | ||

| 0x50 || RW || CLOCK || zegar | | 0x50 || RW || CLOCK || zegar | ||

| Linia 89: | Linia 213: | ||

| 0x52 || RW || CLUSA || dzielnik dla USART (we=1536kHz, wy=153,6kHz) | | 0x52 || RW || CLUSA || dzielnik dla USART (we=1536kHz, wy=153,6kHz) | ||

|- | |- | ||

| | | 0x53 || W || CLCON || sterowanie | ||

|- | |- | ||

| | | align="center" bgcolor="Cornsilk" colspan="4" | <b>DMA</b> | ||

|- | |- | ||

| | | 0x64-0x65 || RW || DMAD1 || kanał 1: rejestr adresu | ||

|- | |- | ||

| | | 0x66-0x67 || RW || DMCO1 || kanał 1: licznik, typ pracy | ||

|- | |- | ||

| | | 0x68-0x69 || RW || DMAD2 || kanał 2: rejestr adresu | ||

|- | |- | ||

| | | 0x6a-0x6b || RW || DMCO2 || kanał 2: licznik, typ pracy | ||

|- | |- | ||

| 0x70 || RW || DMAST || | | 0x6c-0x6d || RW || DMAD3 || kanał 3: rejestr adresu | ||

|- | |||

| 0x6e-0x6f || RW || DMCO3 || kanał 3: licznik, typ pracy | |||

|- | |||

| 0x70 || RW || DMAST || sterowanie | |||

|- | |||

| align="center" bgcolor="Cornsilk" colspan="4" | <b>Linie szeregowe...</b> | |||

|- | |- | ||

| 0x80 || RW || INFTR || informacja do/z linii szeregowej | | 0x80 || RW || INFTR || informacja do/z linii szeregowej | ||

|- | |- | ||

| 0x81 || RW || INFST || status i sterowanie linii szeregowej | | 0x81 || RW || INFST || status i sterowanie linii szeregowej | ||

|- | |||

| align="center" bgcolor="Cornsilk" colspan="4" | <b>...lub inie równoległe</b> | |||

|- | |- | ||

| 0x80 || RW || PARIO || PORT A = parzysty nr. linii | | 0x80 || RW || PARIO || PORT A = parzysty nr. linii | ||

| Linia 118: | Linia 250: | ||

|} | |} | ||

= Urządzenia = | |||

== Timer 8253 == | |||

* Counter 2 | |||

** używany jako dzielnik częstotliwości dla USART | |||

** 16-bit, tryb pracy 3 (Square Wave) | |||

** częstotliwość wejściowa 1536kHz | |||

** częstotliwość wyjściowa 153.6kHz (1536kHz/10) | |||

* Counter 1 | |||

** używany jako dzielnik zegara dla Counter-a 0 (wyjście Counter 1 jest wejściem Counter 0) | |||

** 16-bit, tryb pracy 2 (Rate Generator) | |||

** częstotliwość wejściowa 1536kHz | |||

** częstotliwość wyjściowa 1kHz (1536kHz/1536) | |||

* Counter 0 | |||

** używany do generowania co pół sekundy przerwania zegarowego dla CPU (tam używane do realizacji timeoutów przesyłu, etc.) | |||

** 16-bit, tryb pracy 0 (Interrupt on Terminal Count) | |||

** częstotliwość wejściowa 1kHz | |||

** częstotliwość przerwania 2Hz (1kHz/500), licznik ustawiany ponownie w procedurze obsługi przerwania | |||

== Winchester == | |||

Dyski Winchester adresowane są logicznie, geometria napędu jest ukryta przed użytkownikiem. W pierwszej wersji MULTIX-a obsługującej dyski twarde Winchester wspierane były tylko jednostki o pojemności do 32MB - pole używane do adresowania sektorów miało długość 16-bit. Znane były MULTIX-owi jedynie dwa typy dysków: NEC D5126 (4 powierzchnie) i BASF 6185 (6 powierzchni). Na stałe określona jest ilość sektorów na ścieżkę - 16. Ponieważ dyski pozwalały na umieszczenie 17 sektorów na ścieżce, 6% pojemności napędu było tracone. | |||

W późniejszej wersji pole adresowe dla sektorów zostało rozszerzone do 24-bit, pozwalając na zaadresowanie 8GB (w teorii, ponieważ kontroler nie dawał takiej możliwości). Dzięki możliwości dowolnego określenia liczby powierzchni, wsparcie otrzymały też inne typy dysków (jednak wciąż zachowane zostało sztywne ograniczenie do 16 sektorów na ścieżkę). MULTIX nie znał ilości cylindrów dla danego dysku - próba odczytu/zapisu sektora znajdującego się na nieistniejących cylindrów kończyła się niepowodzeniem. | |||

=== Linia fizyczna === | |||

Kierunek linii fizycznej dla winchesterów musiał mieć wartość 0, inne były traktowane jako nieprawidłowe. | |||

=== Linia logiczna === | |||

Pole konfiguracji winchestera dla "starego" MULTIX-a: | |||

{| class="wikitable" style="text-align: center;" | |||

| width=15 | 0 || width=15 | 1 || width=15 | 2 || width=15 | 3 || width=15 | 4 || width=15 | 5 || width=15 | 6 || width=15 | 7 || width=15 | 8 || width=15 | 9 || width=15 | 10 || width=15 | 11 || width=15 | 12 || width=15 | 13 || width=15 | 14 || width=15 | 15 | |||

|- | |||

| colspan="8" | Typ dysku || colspan="8" | Protekcja format. | |||

|} | |||

Gdzie ''Typ dysku'' to 0 (BASF) lub 1 (NEC). | |||

Pole konfiguracji winchestera dla "nowego" MULTIX-a: | |||

{| class="wikitable" style="text-align: center;" | |||

| width=15 | 0 || width=15 | 1 || width=15 | 2 || width=15 | 3 || width=15 | 4 || width=15 | 5 || width=15 | 6 || width=15 | 7 || width=15 | 8 || width=15 | 9 || width=15 | 10 || width=15 | 11 || width=15 | 12 || width=15 | 13 || width=15 | 14 || width=15 | 15 | |||

|- | |||

| colspan="4" | || Z || colspan="3" | L. pow. || colspan="8" | Protekcja form. | |||

|} | |||

Gdzie ''Z'' jest opisem formatu pola zapasowego. Nazwa ta jest nieco myląca, ponieważ mówi ono o długości numeru sektora w operacjach transmisji i jego znaczenie jest następujące: | |||

* "0" - numer sektora na 2 bajty (max. pojemność dysku 32MB) | |||

* "1" - numer sektora ma 3 bajty (max. teoretyczna pojemność dysku 8GB) | |||

Dla dysków montowanych w "nowym" MULTIX-ie powinno ono być ustawione następująco: | |||

* 0 - dla dysków używanych wcześniej w starym MULTIX-ie | |||

* 1 - dysk >32MB w nowym MULTIX-ie | |||

* 1 lub 0 - dysk <32MB w nowym MULTIX-ie | |||

Pole "protekcja formatowania" jest przez firmware najnowszej wersji MULTIX-a ignorowane. | |||

Obszar zapasowy (do przenoszenia uszkodzonych sektorów) ma zawsze długość ''ilość powierzchni * 16'' sektorów (czyli cały pierwszy cylinder). | |||

=== Operacje === | |||

Maksymalna długość transmisji wynosi 16 sektorów (z punktu widzenia MERY? czy z punktu widzenia zadania mx?). Linie z Winchesterem nie obsługują polecenia "przerwij transmisję". | |||

=== Sektory zapasowe === | |||

Producenci dysków winchester dopuszczali zazwyczaj występowanie na powierzchni dysku | |||

kilkudziesięciu uszkodzonych sektorów. Wyjątkiem był pierwszy cylinder, który | |||

musiał być wolny od błędów. Fakt ten został przez Amepol wykorzystany do | |||

podniesienia niezawodności dysków winchester pracujących w MULTX-ie. | |||

Cały pierwszy cylinder zarezerwowany jest na kopie uszkodzonych sektorów | |||

i jest dla użytkownika niedostępny. Dwa pierwsze sektory zajęte są przez | |||

tablicę numerów uszkodzonych sektorów (pierwszy sektor) i jej wierną kopię (drugi | |||

sektor). Przy czterech głowicach i 16 sektorach na ścieżkę daje to możliwość zrelokowania do 62 sektorów. | |||

Tablica numerów sektorów ma również 62 pozycje. W zależności od wersji MULTIX-a mają one długość 2 lub 3 bajtów. Każda z nich wskazuje, jaki | |||

sektor (o jakim numerze logicznym) został przeniesiony na daną pozycję obszaru | |||

zapasowego. | |||

Jeśli podczas operacji czytania sektora z dysku wystąpił jeden z warunków: | |||

* pole adresowe sektora nie zostało odnalezione | |||

* sektor oznaczony jest jako uszkodzony | |||

to następuje próba odnalezienia danego sektora w obszarze zapasowym. | |||

Jeśli sektor zostanie znaleziony, to jest stamtąd odczytywany i błąd odczytu nie występuje. | |||

Jeśli sektor nie zostanie odnaleziony, to sygnalizowany jest błąd. | |||

Przenoszenie uszkodzonych sektorów do obszaru zapasowego nie jest wykonywane | |||

automatycznie przez MULTIX-a. Odbywa się za | |||

pomocą polecenia formatowania ścieżki z przeniesieniem uszkodzonych sektorów. | |||

== Floppy == | |||

Użyty kontroler napędów Zilog Z0765A08PSC pozwala na podłączenie do czterech napędów dyskietek. MULTIX rozróżnia trzy typy napędów o następujących parametrach zapisanych w tablicy TATYF (TAblica TYpów Flopów): | |||

{| class="wikitable" style="text-align: center;" | |||

! Typ !! Nazwa !! L. głowic !! L. cylindrów !! SRT !! HLT | |||

|- | |||

| 0 || SD || 1 || 40 || 0xCF || 9<<1 | |||

|- | |||

| 1 || DD || 1 || 80 || 0xCF || 9<<1 | |||

|- | |||

| 2 || DD/HD || 1 || 80 || 0x8F || 18<<1 | |||

|} | |||

Gdzie SRT i HLT to następujące parametry kontrolera: | |||

* HLT - Head Load Time (2-254ms co 2ms) | |||

* SRT - Step Rate Time (1-16ms co 1ms) | |||

Niezależnie od typu napędu, rozróżniane są jeszcze (i weryfikowane z typem napędu) typy dyskietek. Ich parametry podawane są podczas operacji "dołącz". | |||

= Inicjalizacja = | |||

Wstępna inicjalizacja MULTIX-a trwał około 500ms (+185ms zerowania pamięci w SINSP) i przebiega następująco: | |||

* zablokuj przerwania | |||

* czy "koniec ROM" wypełniony? | |||

* sprawdzenie sumy kontrolnej ROM | |||

* testowanie RAM (tylko podstawowe 16KB, RAM flopa i winchestera nie są testowane) | |||

* konfiguruj timer, DMA | |||

* odblokuj przerwania | |||

* wołaj SINSP(IWYZE) | |||

W przypadku wystąpienia błędu na dowolnym etapie inicjalizacji, do obu procesorów wysyłane jest przerwanie INSKA z numerem linii wskazującym przyczynę. Praca MULTIX-a jest zatrzymywana i może zostać wznowiona jedynie resetem bądź restartem. | |||

= Przerwania wewnętrzne = | = Przerwania wewnętrzne = | ||

| Linia 129: | Linia 390: | ||

|- | |- | ||

| 3 || IOPRQ || zgłoszenie OPRQ || zapis "KOPRQ" | | 3 || IOPRQ || zgłoszenie OPRQ || zapis "KOPRQ" | ||

|- | |||

| 3 || IFLO8 || floppy (nowszy multix?) | |||

|- | |||

| 4 || INUS4 || nie używane (stary multix) | |||

|- | |- | ||

| 4.5 || ITRAP || dla testowania || odczyt "PTRAP" | | 4.5 || ITRAP || dla testowania || odczyt "PTRAP" | ||

|- | |||

| 5 || INUS5 || nie używane (stary multix) | |||

|- | |||

| 5 || IWIN6 || winchester (nowy multix) | |||

|- | |- | ||

| 5.5 || IPOST || polecenie sterujące || odczyt "POLST+1" | | 5.5 || IPOST || polecenie sterujące || odczyt "POLST+1" | ||

| Linia 147: | Linia 416: | ||

Przerwania wysyłane do MERY-400 opisane są [[Styk programowy MERA-MULTIX#Przerwania|tutaj]]. Rzeczy, o których wspomniana dokumentacja nie mówi: | Przerwania wysyłane do MERY-400 opisane są [[Styk programowy MERA-MULTIX#Przerwania|tutaj]]. Rzeczy, o których wspomniana dokumentacja nie mówi: | ||

Kolejka przerwań wysyłanych z MULTIX-a do MERY-400 | Kolejka przerwań wysyłanych z MULTIX-a do MERY-400 (KOINM) marozmiar RKOIN=32 pozycje i wygląda następująco: | ||

* 0 - pozycja zgłoszonego przerwania | |||

* +1 - ilość oczekujących przerwań | |||

* +2*RKOIN - bufor przerwań, zawiera pary: | |||

** +0 = 0,<specyfikacja> lub 1,<nr proc.>,<specyfikacja> | |||

** +1 = nr linii | |||

ID linii dla przerwania "niesprawny kanał" zawiera informację o przyczynie niesprawności: | ID linii dla przerwania "niesprawny kanał" zawiera informację o przyczynie niesprawności: | ||

| Linia 183: | Linia 458: | ||

|- | |- | ||

| IEPSF || 42 || nieznane polecenie sterujące, KOD=F | | IEPSF || 42 || nieznane polecenie sterujące, KOD=F | ||

|} | |||

= Polecenia = | |||

Rozkazy wejścia-wyjścia wydawane przez jednostkę centralną dzielą się z punktu widzenia MULTIX-a na trzy grupy: | |||

* rozkazy kanałowe, | |||

* polecenia sterujące ogólne, | |||

* polecenia sterujące liniowe. | |||

W zależności od typu polecenia, jest ono przetwarzane w różnych obszarach MULTIX-a. | |||

== Rozkazy kanałowe == | |||

Rozkazy kanałowe wymagają natychmiastowej odpowiedzi niezależnie od tego, czym aktualnie zajęty jest procesor MULTIX-a. Dlatego realizowane są sprzętowo, na styku MULTIX-interfejs MERY-400. Należą do nich: | |||

# '''Zerowanie''' - realizowane sprzętowo przez reset procesora MULTIX-a i wszystkich układów podległych. MULTIX w ten sam sposób musi reagować na zerowanie komendą IN/OU, programowe (MCL) i sprzętowe (CLEAR). To znaczy, że polecenie zerowania musi być dekodowane sprzętowo "na interfejsie" i skutkować sprzętowym resetem. | |||

# '''Sprawdź istnienie kanału''' - rezultatem tego polecenia jest wysterowanie odpowiedzi OK na szynie magistrali. | |||

# '''Podaj specyfikację przerwania''' - rezultatu tego polecenia oczekuje się natychmiast po jego wykonaniu (w procedurze obsługi przerwania). | |||

== Polecenia ogólne == | |||

Odbiór polecenia ogólnego realizowany jest sprzętowo: | |||

* polecenie sterujące i jego argument zapamiętywane są w rejestrach sprzętowych na styku MULTIX-a z interfejsem MERY-400, | |||

* do procesora MULTIX-a wysyłane jest przerwanie IPOST (5.5), | |||

* jeśli procesor jest gotów obsłużyć przerwanie, jednostka centralna MERY-400 dostaje odpowiedź OK, a MULTIX odczytuje zawartość rejestrów zawierających polecenie i rozpoczyna jego obsługę. | |||

* jeśli przerwanie nie zostanie przyjęte, to polecenie nie może zostać obsłużone i j.c. MERY-400 (po timeoucie) dostaje odpowiedź EN. | |||

Polecenia ogólne dotyczą sterowania pracą MULTIX-a i obsługiwane są programowo w procedurze obsługi przerwania IPOST. Należą do nich: | |||

# '''Ustaw konfigurację''' - jest to pierwsze polecenie, jakie MULTIX może przyjąć. Zanim nie zostanie poprawnie zakończone, żadne polecenie liniowe nie może zostać wykonane. W trakcie jego realizacji przerwania są zablokowane, więc każde kolejne polecenie "ustaw konfiguracje" wydane przed zakończeniem bieżącego zakończy się sygnałem EN. | |||

# '''Testuj''' - jest to polecenie specjalne, które skutkuje uruchomieniem na procesorze MULTIX-a programu innego niż zapisany w firmware. Pozwala na przeprowadzenie dowolnego testu komputera. | |||

# '''Cofnij przerwanie niepokwitowane do kolejki''' - dotyczy wyłącznie kolejki przerwań do MERY-400 i musi zostać wykonane podczas gdy kolejka nie zmienia swojego stanu. | |||

=== Ustaw konfigurację === | |||

==== Linie fizyczne ==== | |||

Dla poszczególnych urządzeń dozwolone są jedynie następujące kierunki transmisji: | |||

{| class="wikitable" style="text-align:center;" | |||

! !! Brak !! Input !! Output !! Full-duplex !! Half-duplex | |||

|- | |||

| USART synch. || || + || + || + || (+) | |||

|- | |||

| USART asynch. || || + || + || + || (+) | |||

|- | |||

| 8255 || || + || + || || | |||

|- | |||

| Winchester || + || || || || | |||

|- | |||

| Taśma magnetyczna || + || || || || | |||

|- | |||

| Floppy || + || || || || | |||

|- | |||

|} | |||

'''Uwaga:''' kierunek 6 (half-duplex) wydaje się być opcjonalnie dozwolony dla linii USART (zależy od wersji MULTIX-a?) | |||

Niezależnie od tego, czy linia jest konfigurowana jako użyta, czy nie, kierunek transmisji dla urządzenia musi być poprawny. | |||

Linie fizyczne zorganizowane były sprzętowo w pakiety. To wymusza konfigurowanie ich również w grupach po 4 - MULTIX w trakcie ustawiania konfiguracji sprawdza: | |||

* czy pierwszy numer linii w pakiecie jest wielokrotnością 4 | |||

* czy liczba linii danego typu jest wielokrotnością 4 | |||

* czy liczba pakietów kontrolera pamięci taśmowych nie przekracza 1 (maks. 4 napędy taśmowe, choć dokumentacja wspomina o 8 (po cztery przewijaki na dwa obsługiwane formatery). | |||

Jeśli jakieś linie nie są używane, konfiguracja dla nich musi również zostać przygotowana, przy czym bit 3 pola konfiguracji linii fizycznej ("linia użyta") powinien mieć wtedy wartość 0. W przypadku niespełnienia warunków sygnalizowany jest błąd "niekompletny opis linii fizycznej". | |||

==== Linie logiczne ==== | |||

Mimo, że numer linii fizycznej w polu opisu linii logicznej jest 8-bit, to tylko najmłodsze 5 bitów brane jest pod uwagę. Daje to maksymalną liczbę 32 obsługiwanych linii. Starsze bity (bit 8) wykorzystywane są jedynie dla protokołu taśmy. | |||

Dozwolone typy linii fizycznych dla protokołów linii logicznej: | |||

{| class="wikitable" style="text-align:center;" | |||

! !! USART asynch. !! 8255 !! USART synch. !! Winchester !! Taśma !! Floppy | |||

|- | |||

| Czytnik || + || + || || || || | |||

|- | |||

| Dziurkarka || + || + || || || || | |||

|- | |||

| Monitor || + || || || || || | |||

|- | |||

| Czytnik SOM || + || + || || || || | |||

|- | |||

| Dziurkarka SOM || + || + || || || || | |||

|- | |||

| Monitor SOM || + || || || || || | |||

|- | |||

| Winchester || || || || + || || | |||

|- | |||

| Taśma || || || || || + || | |||

|- | |||

| Floppy || || || || || || + | |||

|- | |||

| TTY ITWL || || || || || || | |||

|- | |||

|} | |||

Dla każdego z protokołów zdefiniowane są wymagane kierunki linii fizycznej w postaci maski zapisanej na dwóch bitach: | |||

* DVINP = 01000000 | |||

* DVOUT = 10000000 | |||

Maska ta odpowiada dwóm pierwszym bitom konfiguracji kierunku linii fizycznej: | |||

* 100xxxxx = output | |||

* 010xxxxx = input | |||

* 110xxxxx = input/output half-duplex | |||

* 111xxxxx = input/output full-duplex | |||

Sprawdzenie polega na zweryfikowaniu, czy dla każdego bitu maski kierunków protokołu zapalony jest odpowiadający mu bit konfiguracji kierunków linii fizycznej. Odpowiada to sprawdzeniu, czy spełniony jest warunek: | |||

maska & kierunek_l_fiz == maska | |||

Dla poszczególnych protokołów linii logicznej dozwolone są zatem następujące kierunki linii fizycznych: | |||

{| class="wikitable" style="text-align:center;" | |||

! !! Brak !! Input !! Output !! Full-duplex !! Half-Duplex | |||

|- | |||

| Czytnik || || + || || + || + | |||

|- | |||

| Dziurkarka || || || + || + || + | |||

|- | |||

| Monitor || || || || + || + | |||

|- | |||

| Czytnik SOM || || + || || + || + | |||

|- | |||

| Dziurkarka SOM || || || + || + || + | |||

|- | |||

| Monitor SOM || || || || + || + | |||

|- | |||

| Winchester || + || + || + || + || + | |||

|- | |||

| Taśma || + || + || + || + || + | |||

|- | |||

| Floppy || + || + || + || + || + | |||

|- | |||

| TTY ITWL || || || || || | |||

|- | |||

|} | |||

== Polecenia liniowe == | |||

Polecenia liniowe są przyjmowane na zasadach takich samych jak polecenia ogólne. Obsługa polecenia w przerwaniu IPOST polega na zgłoszeniu nowego zadania liniowego, bądź odrzucenie polecenia (jeśli linia nie istnieje, bądź w linii jest już aktywne, zgłoszone lub zawieszone zadanie). Odrzuceniu polecenia towarzyszy wysłanie stosownego przerwania do MERY-400. Po zgłoszeniu zadania obsługa przerwania się kończy, a zadanie podjąć może manager zadań (główna pętla programowa MULTIX-a). | |||

= Zadania liniowe = | |||

Zadania są przedmiotem pracy MULTIX-a. Zadanie liniowe opisane jest numerem zadania i numerem linii, której dotyczy. Zadanie może stać się gotowe do podjęcia na skutek różnych zdarzeń, takich jak zgłoszenie polecenia przez MERĘ-400, bądź przerwanie od któregoś z urządzeń zewnętrznych lub timera. Zadania wybierane są do obsłużenia przez manager zadań, który cyklicznie przegląda listę zadań, wybierając (według priorytetów) to, którym należy się zająć. | |||

Zadanie aktywne opisuje pole IDZAD, którego kolejne bajty zawierają: | |||

* 0-1: adres pola głównego | |||

* 2-3: adres pola zadania | |||

* 4: numer zadania | |||

* 5: numer linii logicznej | |||

Etapy, przez które może przechodzić zadanie po wydaniu polecenia przez MERĘ-400: | |||

* zignorowane (EN do procesora - przerwanie IPOST w MULTIX-ie zablokowane) | |||

* przyjęte (przez obsługę przerwania IPOST) | |||

* odrzucone (przez obsługę przerwania IPOST) | |||

* zgłoszone (wpisane do tablicy zadań, gotowe do podjęcia przez task manager MULTIX-a) | |||

* zawieszone (oczekuje w tablicy na zdarzenie) | |||

* aktywne (aktualnie działające) | |||

== Zgłoszenie zadania poleceniem liniowym == | |||

Po otrzymaniu polecenia od MERY-400 MULTIX sprawdza, czy może przyjąć polecenie i reaguje odpowiednio do warunków, wysyłając przerwanie odpowiednie dla danego polecenia: | |||

* jeśli konfiguracja MULTIX-a nie jest ustawiona -> '''brak linii''' | |||

* jeśli linii nie ma w konf (nr. linii > MAXLL) - '''brak linii''' | |||

* jeśli konfiguracja MULTIX-a nie jest ustawiona (ponowne sprawdzenie) '''odrzucenie polecenia''' | |||

* jeśli ((b.war & 1) | (b.zaw) != 0) -> '''odrzucenie polecenia'''. Warunek tłumaczy się na: | |||

** jeśli jest już polecenie bezwarunkowego startu zadania (czyli takie polecenie zostało już wydane ???ale jeszcze nie wystartowane???) | |||

** jeśli zadanie jest aktywne | |||

** jeśli zadanie czeka na warunek | |||

* jeśli żadna z powyższych sytuacji nie wystąpiła, zadanie jest zgłaszane: | |||

** opcjonalnie pobierany jest argument zadania (dla zadań, które mają argumenty) | |||

** PZGLI[zadanie] = 1 | |||

** ADPZL[zadanie, linia] |= 1 (zgłoszenie zadania od początku) | |||

Przerwanie potwierdzające odebranie polecenia nie jest wysyłane na etapie jego zgłoszenia, a dopiero po odebraniu zadania przez manager zadań. | |||

== Manager zadań == | |||

Zadania przechowywane są w dwóch tablicach. Pierwsza z nich, PZGLI, wskazuje, czy zadanie danego typu zostało zgłoszone (dla dowolnej linii). Jest to pierwsze kryterium wyboru zadania, według malejących priorytetów jak w tabeli poniżej: | |||

{| class="wikitable" | |||

! Oznaczenie !! Nr !! Opis | |||

|- | |||

| T.STR || 0 || Podaj status | |||

|- | |||

| T.ODL || 1 || Odłącz linię | |||

|- | |||

| T.ORQ || 2 || Zgłość OPRQ | |||

|- | |||

| T.TRA || 3 || Przesyłaj | |||

|- | |||

| T.ABT || 4 || Zerwij transmisję | |||

|- | |||

| T.DOL || 5 || Dołącz linię | |||

|} | |||

Druga tablica (adres w ADPZL) przechowuje opis stanów wszystkich zadań dla każdej z linii. Stan opisują dwa bajty: | |||

* '''bajt zawieszenia''' - ustawiany przez zadanie, opisuje jego stan: | |||

** ustawiony bit 0 mówi, że zadanie jest aktualnie wykonywane | |||

** nie ustawiony bit 0 mówi, że zadanie jest zawieszone (oczekuje na zdarzenie), wtedy bity 7-1 określają przyczynę zawieszenia | |||

* '''bajt warunków''' - ustawiany "z zewnątrz" zadania, opisuje warunki, jakie dla zadania wystąpiły: | |||

** ustawiony bit 0 mówi, że zadanie należy wystartować (rozpocząć) | |||

** bity 7-1 opisują warunki, jakie wystąpiły dla zadania | |||

Jeśli okaże się, że żadna linia nie wymaga obsługi, zgłoszenie zadania jest kasowane. | |||

Po wybraniu typu zadania przeglądane są bajty warunków wszystkich linie (począwszy od linii A+1, gdzie A jest poprzednio obsługiwaną linią). Podejmowana jest obsługa pierwszej linii, która jej wymaga, a wykonywana akcja zależy od tego, jakie zdarzenie nastąpiło w linii. Priorytetem jest zawartość bajtu warunku (od najwyższego priorytetu): | |||

{| class="wikitable" | |||

! Oznaczenie !! Wartość !! Opis | |||

|- | |||

| - || 00000001 || start zadania | |||

|- | |||

| WAODB || 00000010 || przesyłaj - zakończony odbiór | |||

|- | |||

| WANAD || 00000100 || przesyłaj - zakończone nadawanie | |||

|- | |||

| WAAWA || 00001000 || przesyłaj - awaria | |||

|- | |||

| WAOPR || 00010000 || przesyłaj - OPRQ | |||

|- | |||

| WAFWI || 00100000 || przesyłaj - winchester zakończył, XON dla monitorów | |||

|- | |||

| WATIM || 10000000 || przesyłaj - timeout (timer) | |||

|} | |||

Warunek WAFWI dla winchesterów oznacza zwolnienie kontrolera. Kontroler może w danej chwili obsługiwać tylko jeden dysk. Jeśli inna linia (inny winchester) chce transmitować dane, musi poczekać, aż obecnie transmitująca linia zwolni kontroler. | |||

== Odebranie zadania == | |||

* poszukaj w PZGLI zgłoszonego zadania o najwyższym priorytecie | |||

* wpisz nr.zad do IDZAD | |||

* wybierz linię, od której zaczniesz szukać (następna, bądź 0 jeśli pracowała ostatnia) i iteruj po wszystkich liniach | |||

** jeśli dla żadnej linii nie znaleziono zgłoszenia -> zeruj zgłoszenia zadania dla wszystkich linii | |||

** jeśli dla linii jest jakieś zgłoszenie -> startuj zadanie | |||

** wyślij przerwanie liniowe | |||

** ponownie uruchom manager zadań | |||

== Status linii == | |||

Polecenie liniowe "podaj status" zwraca status linii opisany strukturą STATL. Dokumentacja opisuje znaczenie tylko niektórych jej bitów, poniżej kompletny opis dwóch bajtów składających się na status. Numeracja bitów MERY-400 (0=MSB, 15=LSB). W słowie statusu jest jeszcze trzeci bajt, niedostępny dla programisty, opisujący status USART-a. | |||

{| class="wikitable" | |||

! Bit !! Opis | |||

|- | |||

| 0 || 0 | |||

|- | |||

| 1 || Nadawanie ostatniego fragmentu | |||

|- | |||

| 2 || Nadawanie zawieszone przez XOFF | |||

|- | |||

| 3 || Zadanie zawieszone przez XOFF | |||

|- | |||

| 4 || - | |||

|- | |||

| 5 || - | |||

|- | |||

| 6 || Aktywna transmisja | |||

|- | |||

| 7 || Linia dołączona | |||

|- | |||

| 8 || OPRQ | |||

|- | |||

| 9 || Błąd parzystości | |||

|- | |||

| 10 || Odebrano znak kończący | |||

|- | |||

| 11 || Stop po CAN (protokół 5) | |||

|- | |||

| 12 || Odbiór w toku | |||

|- | |||

| 13 || Odbiór rozpoczęty | |||

|- | |||

| 14 || Nadawanie w toku | |||

|- | |||

| 15 || Nadawanie rozpoczęte | |||

|} | |} | ||

Aktualna wersja na dzień 17:34, 28 mar 2018

Dokumentacja techniczna MULTIX-a prawdopodobnie dziś już nie istnieje. Niniejsza strona jest próbą odtworzenia tego, jak MULTIX działał i jaka była jego architektura.

Sprzęt

MULTIX to komputer zbudowany w oparciu o procesor Intel 8085, z programem sterującym (firmware) zapisanym w pamięci ROM. Z punktu widzenia MULTIX-a MERA-400 jest jednym z jego urządzeń zewnętrznych, widzianym przez pryzmat sprzęgu znajdującego się pomiędzy magistralami MERY-400 a MULTIX-a.

Komunikacja MERY-400 z MULTIX-em odbywa się przy użyciu:

- jednego z przerwań procesora 8085, które informuje o nadejściu polecenia wysłanego rozkazami IN/OU z MERY-400

- rejestrów sprzętowych sprzęgu przechowujących odczytane z magistrali MERY-400 argumenty polecenia IN/OU

Komunikacja MULTIX-a z MERĄ-400 odbywa się przy użyciu:

- odczytu/zapisu pamięci MERY-400 (przy użyciu kontrolera DMA)

- zgłoszenia przerwania kanałowego do MERY-400

Poniższy schemat blokowy przedstawia budowę MULTIX-a (wraz z podziałem na pakiety) i sprzęg z MERĄ-400.

Pakiety

Bloki funkcjonalne MULTIX-a i kontrolery urządzeń wejścia/wyjścia rozlokowane są na "wąskich" pakietach MERY-400.

ME-MIK-400

ME-MIK-400 to pakiet mikrokomputera zawierający:

- CPU: 8085 3MHz (NEC D8085AC)

- pamięć EPROM 3x8KB

- pamięć RAM 2x8KB Hitachi HM6264LP-15

- Timer: 8253 (NEC M5L8253P-5)

- DMA: 8257 (NEC D8257C-2)

- kanał 1: MERA-400

- kanał 2: taśma

- kanał 3: autoload

ME-BI-400 i ME-BM-400

ME-BI-400 i ME-BM-400 to pakiety sprzęgu zapewniające komunikację między MULTIX-em a MERĄ-400. Realizują one m.in. następujące funkcje:

- Od strony interfejsu MERY-400:

- dekodowanie i realizację krytycznych rozkazów I/O

- zgłaszanie przerwania kanałowego

- transmisję danych do/z PAO

- Od strony MULTIX-a:

- sprzętowe rejestry I/O

- reset MULTIX-a i urządzeń podległych

- zarządzanie przerwaniem "polecenie sterujące"

ME-UTR-400

Cztery porty równoległe zrealizowane na dwóch układach 8255 (NEC D8255AC-2). Pakiet występuje w wersjach ME-UTR-1, ME-UTR-2 i ME-UTR-3, pozwalających na podłączenie różnego rodzaju urządzeń równoległych

ME-UTS-400

Cztery porty szeregowe zrealizowane na czterech układach 8251 (NEC M5L8251AP-5). Pakiet występuje w wersjach ME-UTS-1, ME-UTS-2 i ME-UTS-3, pozwalających na podłączenie urządzeń różnymi interfejsami (V24 lub prądowym z optoizolacją) i dających różne dodatkowe możliwości ich konfiguracji.

ME-FDC

Kontroler czterech stacji dyskietek zrealizowany w oparciu o:

- kontroler Zilog Z0765A08PSC

- DMA 8257 (NEC M5L8257P-5)

- pamięć RAM 8KB Hitachi HM6264LP-15

ME-WDC-506

Kontroler czterech dysków ST-506 (winchester) zrealizowany w oparciu o:

- kontroler Intel C82062-00

- pamięć RAM 8KB Hitachi HM6264LP-15

Mapa pamięci

| Adres | Nazwa | Zawartość |

|---|---|---|

| 0x0000-0x1fff | EPROM 1 | |

| 0x2000-0x3fff | EPROM 2 | |

| 0x4000-0x5fff | EPROM 3 | |

| 0x6000-0x9fff | RAM | RAM główna (16KB) |

| 0x6000+154 | STACK | koniec stosu, początek dostępnej RAM |

| 0xa000-0xbfff | RAMW8 | RAM floppy dysku (8KB) |

| 0xc000-0xdfff | RAMW6 | RAM winchestera (8KB) |

| 0xff00-0xffff | AD | we/wy widziane jako pamięć |

| Adres | Nazwa | Zawartość |

|---|---|---|

| 0-2 | JMP IZER | |

| 3 | 0 | |

| 4 | suma kontrolna ROM | |

| 5-6 | ostatni adres ROM | |

| 7 | ? | |

| 8-0x3f | przerwania 8085 | |

| 0x4f | BEGPR | początek programu |

| 0x6000 | RAM | POCZATEK RAM |

| 0x6000-0x6020 | tablica przerwań (ZAWIERA: JMP <ADRES>) | |

| 0x6000 | JMP IKWIT - 1 | |

| 0x6003 | JMP IZEGA - 2 | |

| 0x6006 | JMP IOPRQ - 3 | |

| 0x6009 | JMP INUS4 - 4 | |

| 0x600c | JMP ITRAP - 4.5 | |

| 0x600f | JMP IWINC - 5 | |

| 0x6012 | JMP IPOST - 5.5 | |

| 0x6015 | JMP ITAPE - 6 | |

| 0x6018 | JMP IKASE - 6.5 | |

| 0x601b | JMP IKAPA - 7 | |

| 0x601e | JMP IDMA - 7.5 | |

| 0x6021 | NUPRO | NR PROCESORA DLA <SETKO> |

| 0x6022 | STBOT | dno stosu |

| 0x609a | STACK = RAM+154 | KONIEC STOSU=POCZATEK DOSTEPNEJ RAM |

| 0x609a-0x609b | FINRA | ostatni adres sprawnej RAM |

| 0x609c | RAM00 | początek pamięci zerowanej |

| 0x60a3-0x60a4 | RAMUS | adres wykorzystanej ram +1 |

I/O

Rejestry I/O z punktu widzenia MULTIX-a mogą być używane do:

- odczytu lub zapisu (R, W)

- tylko odczytu (R)

- sterowania (S)

Operacje odczytu i zapisu są intuicyjne, natomiast sterowanie ma następujący przebieg:

- MULTIX wykonuje operację odczytu (IN) na rejestrze

- Sprzęg MULTIX-MERA wykonuje operację właściwą dla funkcji rejestru (np. zgłasza przerwanie do procesora)

- W akumulatorze zwracany jest rezultat wykonanej przez sprzęg operacji (wartość różna w zależności od rejestru, oznaczająca np.: OK, błąd parzystości, etc.)

| Adres | R/W/S | Nazwa | Znaczenie |

|---|---|---|---|

| MERA-400 | |||

| 0-1 | R | DANEI | dane odczytane z MERA-400 (MSB, LSB) |

| 0-1 | W | DANEO | dane do przesłania rozkazem "pisz do PAO" (MSB, LSB) |

| 2-3 | R | PSARG | argument polecenia sterującego (MSB, LSB) |

| 2-3 | W | ADRES | adres w PAO MERA-400 (MSB, LSB) |

| 4 | R | POLST | specyfikacja polecenia sterującego |

| 4 | W | NBPN | nr bloku PAO, nr procesora |

| 5 | R | POLST+1 | ID linii |

| 5 | W | KWINT | pokwitowanie przerwań |

| 6 | W | SPECI | specyfikacja przerwania do MERA-400 |

| 7 | W | SPECI+1 | specyfikacja przerwania: numer linii |

| 8 | S | KOTRA | Rozkaz "koniec transmisji" |

| 10 | S | PISZB | Rozkaz "pisz blok przez DMA do MERA-400" |

| 11 | S | CZYTB | Rozkaz "czytaj blok przez DMA z MERA-400" |

| 12 | S | PISZP | Rozkaz "pisz do MERA-400" |

| 13 | S | CZYTP | Rozkaz "czytaj z MERA-400" |

| 14 | S | INTR0 | Rozkaz "zgłoś przerwanie do MERA-400" (procesor 0) |

| 15 | S | INTR1 | Rozkaz "zgłoś przerwanie do MERA-400" (procesor 1) |

| 0x38 | W | KOPRQ | pokwitowanie OPRQ |

| 0x4e | W | WUUPG | ustawienie maski przerwań 'INTR' |

| Timer | |||

| 0x50 | RW | CLOCK | zegar |

| 0x51 | RW | CLDZI | dzielnik zegara (we=1536kHz) |

| 0x52 | RW | CLUSA | dzielnik dla USART (we=1536kHz, wy=153,6kHz) |

| 0x53 | W | CLCON | sterowanie |

| DMA | |||

| 0x64-0x65 | RW | DMAD1 | kanał 1: rejestr adresu |

| 0x66-0x67 | RW | DMCO1 | kanał 1: licznik, typ pracy |

| 0x68-0x69 | RW | DMAD2 | kanał 2: rejestr adresu |

| 0x6a-0x6b | RW | DMCO2 | kanał 2: licznik, typ pracy |

| 0x6c-0x6d | RW | DMAD3 | kanał 3: rejestr adresu |

| 0x6e-0x6f | RW | DMCO3 | kanał 3: licznik, typ pracy |

| 0x70 | RW | DMAST | sterowanie |

| Linie szeregowe... | |||

| 0x80 | RW | INFTR | informacja do/z linii szeregowej |

| 0x81 | RW | INFST | status i sterowanie linii szeregowej |

| ...lub inie równoległe | |||

| 0x80 | RW | PARIO | PORT A = parzysty nr. linii |

| 0x81 | RW | PARIO+1 | PORT B = nieparzysty nr. linii |

| 0x82 | RW | PARIO+2 | port C = sygnały handshake i gotowości |

| 0x83 | R | PARIO+3 | sterowanie |

| ... | ... | ... | kolejne linie szeregowe/równoległe |

Urządzenia

Timer 8253

- Counter 2

- używany jako dzielnik częstotliwości dla USART

- 16-bit, tryb pracy 3 (Square Wave)

- częstotliwość wejściowa 1536kHz

- częstotliwość wyjściowa 153.6kHz (1536kHz/10)

- Counter 1

- używany jako dzielnik zegara dla Counter-a 0 (wyjście Counter 1 jest wejściem Counter 0)

- 16-bit, tryb pracy 2 (Rate Generator)

- częstotliwość wejściowa 1536kHz

- częstotliwość wyjściowa 1kHz (1536kHz/1536)

- Counter 0

- używany do generowania co pół sekundy przerwania zegarowego dla CPU (tam używane do realizacji timeoutów przesyłu, etc.)

- 16-bit, tryb pracy 0 (Interrupt on Terminal Count)

- częstotliwość wejściowa 1kHz

- częstotliwość przerwania 2Hz (1kHz/500), licznik ustawiany ponownie w procedurze obsługi przerwania

Winchester

Dyski Winchester adresowane są logicznie, geometria napędu jest ukryta przed użytkownikiem. W pierwszej wersji MULTIX-a obsługującej dyski twarde Winchester wspierane były tylko jednostki o pojemności do 32MB - pole używane do adresowania sektorów miało długość 16-bit. Znane były MULTIX-owi jedynie dwa typy dysków: NEC D5126 (4 powierzchnie) i BASF 6185 (6 powierzchni). Na stałe określona jest ilość sektorów na ścieżkę - 16. Ponieważ dyski pozwalały na umieszczenie 17 sektorów na ścieżce, 6% pojemności napędu było tracone.

W późniejszej wersji pole adresowe dla sektorów zostało rozszerzone do 24-bit, pozwalając na zaadresowanie 8GB (w teorii, ponieważ kontroler nie dawał takiej możliwości). Dzięki możliwości dowolnego określenia liczby powierzchni, wsparcie otrzymały też inne typy dysków (jednak wciąż zachowane zostało sztywne ograniczenie do 16 sektorów na ścieżkę). MULTIX nie znał ilości cylindrów dla danego dysku - próba odczytu/zapisu sektora znajdującego się na nieistniejących cylindrów kończyła się niepowodzeniem.

Linia fizyczna

Kierunek linii fizycznej dla winchesterów musiał mieć wartość 0, inne były traktowane jako nieprawidłowe.

Linia logiczna

Pole konfiguracji winchestera dla "starego" MULTIX-a:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| Typ dysku | Protekcja format. | ||||||||||||||

Gdzie Typ dysku to 0 (BASF) lub 1 (NEC).

Pole konfiguracji winchestera dla "nowego" MULTIX-a:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| Z | L. pow. | Protekcja form. | |||||||||||||

Gdzie Z jest opisem formatu pola zapasowego. Nazwa ta jest nieco myląca, ponieważ mówi ono o długości numeru sektora w operacjach transmisji i jego znaczenie jest następujące:

- "0" - numer sektora na 2 bajty (max. pojemność dysku 32MB)

- "1" - numer sektora ma 3 bajty (max. teoretyczna pojemność dysku 8GB)

Dla dysków montowanych w "nowym" MULTIX-ie powinno ono być ustawione następująco:

- 0 - dla dysków używanych wcześniej w starym MULTIX-ie

- 1 - dysk >32MB w nowym MULTIX-ie

- 1 lub 0 - dysk <32MB w nowym MULTIX-ie

Pole "protekcja formatowania" jest przez firmware najnowszej wersji MULTIX-a ignorowane.

Obszar zapasowy (do przenoszenia uszkodzonych sektorów) ma zawsze długość ilość powierzchni * 16 sektorów (czyli cały pierwszy cylinder).

Operacje

Maksymalna długość transmisji wynosi 16 sektorów (z punktu widzenia MERY? czy z punktu widzenia zadania mx?). Linie z Winchesterem nie obsługują polecenia "przerwij transmisję".

Sektory zapasowe

Producenci dysków winchester dopuszczali zazwyczaj występowanie na powierzchni dysku kilkudziesięciu uszkodzonych sektorów. Wyjątkiem był pierwszy cylinder, który musiał być wolny od błędów. Fakt ten został przez Amepol wykorzystany do podniesienia niezawodności dysków winchester pracujących w MULTX-ie.

Cały pierwszy cylinder zarezerwowany jest na kopie uszkodzonych sektorów i jest dla użytkownika niedostępny. Dwa pierwsze sektory zajęte są przez tablicę numerów uszkodzonych sektorów (pierwszy sektor) i jej wierną kopię (drugi sektor). Przy czterech głowicach i 16 sektorach na ścieżkę daje to możliwość zrelokowania do 62 sektorów.

Tablica numerów sektorów ma również 62 pozycje. W zależności od wersji MULTIX-a mają one długość 2 lub 3 bajtów. Każda z nich wskazuje, jaki sektor (o jakim numerze logicznym) został przeniesiony na daną pozycję obszaru zapasowego.

Jeśli podczas operacji czytania sektora z dysku wystąpił jeden z warunków:

- pole adresowe sektora nie zostało odnalezione

- sektor oznaczony jest jako uszkodzony

to następuje próba odnalezienia danego sektora w obszarze zapasowym. Jeśli sektor zostanie znaleziony, to jest stamtąd odczytywany i błąd odczytu nie występuje. Jeśli sektor nie zostanie odnaleziony, to sygnalizowany jest błąd.

Przenoszenie uszkodzonych sektorów do obszaru zapasowego nie jest wykonywane automatycznie przez MULTIX-a. Odbywa się za pomocą polecenia formatowania ścieżki z przeniesieniem uszkodzonych sektorów.

Floppy

Użyty kontroler napędów Zilog Z0765A08PSC pozwala na podłączenie do czterech napędów dyskietek. MULTIX rozróżnia trzy typy napędów o następujących parametrach zapisanych w tablicy TATYF (TAblica TYpów Flopów):

| Typ | Nazwa | L. głowic | L. cylindrów | SRT | HLT |

|---|---|---|---|---|---|

| 0 | SD | 1 | 40 | 0xCF | 9<<1 |

| 1 | DD | 1 | 80 | 0xCF | 9<<1 |

| 2 | DD/HD | 1 | 80 | 0x8F | 18<<1 |

Gdzie SRT i HLT to następujące parametry kontrolera:

- HLT - Head Load Time (2-254ms co 2ms)

- SRT - Step Rate Time (1-16ms co 1ms)

Niezależnie od typu napędu, rozróżniane są jeszcze (i weryfikowane z typem napędu) typy dyskietek. Ich parametry podawane są podczas operacji "dołącz".

Inicjalizacja

Wstępna inicjalizacja MULTIX-a trwał około 500ms (+185ms zerowania pamięci w SINSP) i przebiega następująco:

- zablokuj przerwania

- czy "koniec ROM" wypełniony?

- sprawdzenie sumy kontrolnej ROM

- testowanie RAM (tylko podstawowe 16KB, RAM flopa i winchestera nie są testowane)

- konfiguruj timer, DMA

- odblokuj przerwania

- wołaj SINSP(IWYZE)

W przypadku wystąpienia błędu na dowolnym etapie inicjalizacji, do obu procesorów wysyłane jest przerwanie INSKA z numerem linii wskazującym przyczynę. Praca MULTIX-a jest zatrzymywana i może zostać wznowiona jedynie resetem bądź restartem.

Przerwania wewnętrzne

| Nr | Oznaczenie | Opis | Pokwitowanie |

|---|---|---|---|

| 1 | IKWIT | MERA-400 przyjęła przerwanie | zapis 1 DO "KWINT" |

| 2 | IZEGA | zegar | zapis "MODE" do "CLCON" |

| 3 | IOPRQ | zgłoszenie OPRQ | zapis "KOPRQ" |

| 3 | IFLO8 | floppy (nowszy multix?) | |

| 4 | INUS4 | nie używane (stary multix) | |

| 4.5 | ITRAP | dla testowania | odczyt "PTRAP" |

| 5 | INUS5 | nie używane (stary multix) | |

| 5 | IWIN6 | winchester (nowy multix) | |

| 5.5 | IPOST | polecenie sterujące | odczyt "POLST+1" |

| 6 | ITAP | taśma magnetyczna | odczyt specyfikacji |

| 6.5 | IKASE | kaskada serial | odczyt/zapis informacji |

| 7 | IKAPA | kaskada parallel | odczyt/zapis informacji |

| 7.5 | IDMA | DMA | odczyt DMAST |

Przerwania do MERA-400

Przerwania wysyłane do MERY-400 opisane są tutaj. Rzeczy, o których wspomniana dokumentacja nie mówi:

Kolejka przerwań wysyłanych z MULTIX-a do MERY-400 (KOINM) marozmiar RKOIN=32 pozycje i wygląda następująco:

- 0 - pozycja zgłoszonego przerwania

- +1 - ilość oczekujących przerwań

- +2*RKOIN - bufor przerwań, zawiera pary:

- +0 = 0,<specyfikacja> lub 1,<nr proc.>,<specyfikacja>

- +1 = nr linii

ID linii dla przerwania "niesprawny kanał" zawiera informację o przyczynie niesprawności:

- 1 - błąd sumy kontrolnej ROM

- 3 - za mała pamięć RAM

- 5 - przesunięcie SP

- 11 - RST 4

- 13 - RST 5 gdy WIN=0

- 15 - RST 6 gdy TAP=0

- 17 - niekompletny program: brak 5 (koniec RAM), SETKO, TESTU

- 19 - błąd transmisji przy POST-MORT po ITRAP

- 2*N dla N=0-32 - niedozwolona specyfikacja przerwania linii fizycznej nr N, gdzie:

- (STBOT) - adres ostatniej pozycji stosu

- ostatnia pozycja - 2*N, specyfikacja

Przerwania, o których nie wspomina dokumentacja:

| Oznaczenie | Nr | Opis |

|---|---|---|

| IEPS0 | 35 | nieznane polecenie sterujące, KOD=0 |

| IEPS6 | 36 | nieznane polecenie sterujące, KOD=6 |

| IEPS7 | 37 | nieznane polecenie sterujące, KOD=7 |

| IEPS8 | 38 | nieznane polecenie sterujące, KOD=8 |

| IEPSC | 39 | nieznane polecenie sterujące, KOD=C |

| IEPSD | 40 | nieznane polecenie sterujące, KOD=D |

| IEPSE | 41 | nieznane polecenie sterujące, KOD=E |

| IEPSF | 42 | nieznane polecenie sterujące, KOD=F |

Polecenia

Rozkazy wejścia-wyjścia wydawane przez jednostkę centralną dzielą się z punktu widzenia MULTIX-a na trzy grupy:

- rozkazy kanałowe,

- polecenia sterujące ogólne,

- polecenia sterujące liniowe.

W zależności od typu polecenia, jest ono przetwarzane w różnych obszarach MULTIX-a.

Rozkazy kanałowe

Rozkazy kanałowe wymagają natychmiastowej odpowiedzi niezależnie od tego, czym aktualnie zajęty jest procesor MULTIX-a. Dlatego realizowane są sprzętowo, na styku MULTIX-interfejs MERY-400. Należą do nich:

- Zerowanie - realizowane sprzętowo przez reset procesora MULTIX-a i wszystkich układów podległych. MULTIX w ten sam sposób musi reagować na zerowanie komendą IN/OU, programowe (MCL) i sprzętowe (CLEAR). To znaczy, że polecenie zerowania musi być dekodowane sprzętowo "na interfejsie" i skutkować sprzętowym resetem.

- Sprawdź istnienie kanału - rezultatem tego polecenia jest wysterowanie odpowiedzi OK na szynie magistrali.

- Podaj specyfikację przerwania - rezultatu tego polecenia oczekuje się natychmiast po jego wykonaniu (w procedurze obsługi przerwania).

Polecenia ogólne

Odbiór polecenia ogólnego realizowany jest sprzętowo:

- polecenie sterujące i jego argument zapamiętywane są w rejestrach sprzętowych na styku MULTIX-a z interfejsem MERY-400,

- do procesora MULTIX-a wysyłane jest przerwanie IPOST (5.5),

- jeśli procesor jest gotów obsłużyć przerwanie, jednostka centralna MERY-400 dostaje odpowiedź OK, a MULTIX odczytuje zawartość rejestrów zawierających polecenie i rozpoczyna jego obsługę.

- jeśli przerwanie nie zostanie przyjęte, to polecenie nie może zostać obsłużone i j.c. MERY-400 (po timeoucie) dostaje odpowiedź EN.

Polecenia ogólne dotyczą sterowania pracą MULTIX-a i obsługiwane są programowo w procedurze obsługi przerwania IPOST. Należą do nich:

- Ustaw konfigurację - jest to pierwsze polecenie, jakie MULTIX może przyjąć. Zanim nie zostanie poprawnie zakończone, żadne polecenie liniowe nie może zostać wykonane. W trakcie jego realizacji przerwania są zablokowane, więc każde kolejne polecenie "ustaw konfiguracje" wydane przed zakończeniem bieżącego zakończy się sygnałem EN.

- Testuj - jest to polecenie specjalne, które skutkuje uruchomieniem na procesorze MULTIX-a programu innego niż zapisany w firmware. Pozwala na przeprowadzenie dowolnego testu komputera.

- Cofnij przerwanie niepokwitowane do kolejki - dotyczy wyłącznie kolejki przerwań do MERY-400 i musi zostać wykonane podczas gdy kolejka nie zmienia swojego stanu.

Ustaw konfigurację

Linie fizyczne

Dla poszczególnych urządzeń dozwolone są jedynie następujące kierunki transmisji:

| Brak | Input | Output | Full-duplex | Half-duplex | |

|---|---|---|---|---|---|

| USART synch. | + | + | + | (+) | |

| USART asynch. | + | + | + | (+) | |

| 8255 | + | + | |||

| Winchester | + | ||||

| Taśma magnetyczna | + | ||||

| Floppy | + |

Uwaga: kierunek 6 (half-duplex) wydaje się być opcjonalnie dozwolony dla linii USART (zależy od wersji MULTIX-a?)

Niezależnie od tego, czy linia jest konfigurowana jako użyta, czy nie, kierunek transmisji dla urządzenia musi być poprawny.

Linie fizyczne zorganizowane były sprzętowo w pakiety. To wymusza konfigurowanie ich również w grupach po 4 - MULTIX w trakcie ustawiania konfiguracji sprawdza:

- czy pierwszy numer linii w pakiecie jest wielokrotnością 4

- czy liczba linii danego typu jest wielokrotnością 4

- czy liczba pakietów kontrolera pamięci taśmowych nie przekracza 1 (maks. 4 napędy taśmowe, choć dokumentacja wspomina o 8 (po cztery przewijaki na dwa obsługiwane formatery).

Jeśli jakieś linie nie są używane, konfiguracja dla nich musi również zostać przygotowana, przy czym bit 3 pola konfiguracji linii fizycznej ("linia użyta") powinien mieć wtedy wartość 0. W przypadku niespełnienia warunków sygnalizowany jest błąd "niekompletny opis linii fizycznej".

Linie logiczne

Mimo, że numer linii fizycznej w polu opisu linii logicznej jest 8-bit, to tylko najmłodsze 5 bitów brane jest pod uwagę. Daje to maksymalną liczbę 32 obsługiwanych linii. Starsze bity (bit 8) wykorzystywane są jedynie dla protokołu taśmy.

Dozwolone typy linii fizycznych dla protokołów linii logicznej:

| USART asynch. | 8255 | USART synch. | Winchester | Taśma | Floppy | |

|---|---|---|---|---|---|---|

| Czytnik | + | + | ||||

| Dziurkarka | + | + | ||||

| Monitor | + | |||||

| Czytnik SOM | + | + | ||||

| Dziurkarka SOM | + | + | ||||

| Monitor SOM | + | |||||

| Winchester | + | |||||

| Taśma | + | |||||

| Floppy | + | |||||

| TTY ITWL |

Dla każdego z protokołów zdefiniowane są wymagane kierunki linii fizycznej w postaci maski zapisanej na dwóch bitach:

- DVINP = 01000000

- DVOUT = 10000000

Maska ta odpowiada dwóm pierwszym bitom konfiguracji kierunku linii fizycznej:

- 100xxxxx = output

- 010xxxxx = input

- 110xxxxx = input/output half-duplex

- 111xxxxx = input/output full-duplex

Sprawdzenie polega na zweryfikowaniu, czy dla każdego bitu maski kierunków protokołu zapalony jest odpowiadający mu bit konfiguracji kierunków linii fizycznej. Odpowiada to sprawdzeniu, czy spełniony jest warunek:

maska & kierunek_l_fiz == maska

Dla poszczególnych protokołów linii logicznej dozwolone są zatem następujące kierunki linii fizycznych:

| Brak | Input | Output | Full-duplex | Half-Duplex | |

|---|---|---|---|---|---|

| Czytnik | + | + | + | ||

| Dziurkarka | + | + | + | ||

| Monitor | + | + | |||

| Czytnik SOM | + | + | + | ||

| Dziurkarka SOM | + | + | + | ||

| Monitor SOM | + | + | |||

| Winchester | + | + | + | + | + |

| Taśma | + | + | + | + | + |

| Floppy | + | + | + | + | + |

| TTY ITWL |

Polecenia liniowe

Polecenia liniowe są przyjmowane na zasadach takich samych jak polecenia ogólne. Obsługa polecenia w przerwaniu IPOST polega na zgłoszeniu nowego zadania liniowego, bądź odrzucenie polecenia (jeśli linia nie istnieje, bądź w linii jest już aktywne, zgłoszone lub zawieszone zadanie). Odrzuceniu polecenia towarzyszy wysłanie stosownego przerwania do MERY-400. Po zgłoszeniu zadania obsługa przerwania się kończy, a zadanie podjąć może manager zadań (główna pętla programowa MULTIX-a).

Zadania liniowe

Zadania są przedmiotem pracy MULTIX-a. Zadanie liniowe opisane jest numerem zadania i numerem linii, której dotyczy. Zadanie może stać się gotowe do podjęcia na skutek różnych zdarzeń, takich jak zgłoszenie polecenia przez MERĘ-400, bądź przerwanie od któregoś z urządzeń zewnętrznych lub timera. Zadania wybierane są do obsłużenia przez manager zadań, który cyklicznie przegląda listę zadań, wybierając (według priorytetów) to, którym należy się zająć.

Zadanie aktywne opisuje pole IDZAD, którego kolejne bajty zawierają:

- 0-1: adres pola głównego

- 2-3: adres pola zadania

- 4: numer zadania

- 5: numer linii logicznej

Etapy, przez które może przechodzić zadanie po wydaniu polecenia przez MERĘ-400:

- zignorowane (EN do procesora - przerwanie IPOST w MULTIX-ie zablokowane)

- przyjęte (przez obsługę przerwania IPOST)

- odrzucone (przez obsługę przerwania IPOST)

- zgłoszone (wpisane do tablicy zadań, gotowe do podjęcia przez task manager MULTIX-a)

- zawieszone (oczekuje w tablicy na zdarzenie)

- aktywne (aktualnie działające)

Zgłoszenie zadania poleceniem liniowym

Po otrzymaniu polecenia od MERY-400 MULTIX sprawdza, czy może przyjąć polecenie i reaguje odpowiednio do warunków, wysyłając przerwanie odpowiednie dla danego polecenia:

- jeśli konfiguracja MULTIX-a nie jest ustawiona -> brak linii

- jeśli linii nie ma w konf (nr. linii > MAXLL) - brak linii

- jeśli konfiguracja MULTIX-a nie jest ustawiona (ponowne sprawdzenie) odrzucenie polecenia

- jeśli ((b.war & 1) | (b.zaw) != 0) -> odrzucenie polecenia. Warunek tłumaczy się na:

- jeśli jest już polecenie bezwarunkowego startu zadania (czyli takie polecenie zostało już wydane ???ale jeszcze nie wystartowane???)

- jeśli zadanie jest aktywne

- jeśli zadanie czeka na warunek

- jeśli żadna z powyższych sytuacji nie wystąpiła, zadanie jest zgłaszane:

- opcjonalnie pobierany jest argument zadania (dla zadań, które mają argumenty)

- PZGLI[zadanie] = 1

- ADPZL[zadanie, linia] |= 1 (zgłoszenie zadania od początku)

Przerwanie potwierdzające odebranie polecenia nie jest wysyłane na etapie jego zgłoszenia, a dopiero po odebraniu zadania przez manager zadań.

Manager zadań

Zadania przechowywane są w dwóch tablicach. Pierwsza z nich, PZGLI, wskazuje, czy zadanie danego typu zostało zgłoszone (dla dowolnej linii). Jest to pierwsze kryterium wyboru zadania, według malejących priorytetów jak w tabeli poniżej:

| Oznaczenie | Nr | Opis |

|---|---|---|

| T.STR | 0 | Podaj status |

| T.ODL | 1 | Odłącz linię |

| T.ORQ | 2 | Zgłość OPRQ |

| T.TRA | 3 | Przesyłaj |

| T.ABT | 4 | Zerwij transmisję |

| T.DOL | 5 | Dołącz linię |

Druga tablica (adres w ADPZL) przechowuje opis stanów wszystkich zadań dla każdej z linii. Stan opisują dwa bajty:

- bajt zawieszenia - ustawiany przez zadanie, opisuje jego stan:

- ustawiony bit 0 mówi, że zadanie jest aktualnie wykonywane

- nie ustawiony bit 0 mówi, że zadanie jest zawieszone (oczekuje na zdarzenie), wtedy bity 7-1 określają przyczynę zawieszenia

- bajt warunków - ustawiany "z zewnątrz" zadania, opisuje warunki, jakie dla zadania wystąpiły:

- ustawiony bit 0 mówi, że zadanie należy wystartować (rozpocząć)

- bity 7-1 opisują warunki, jakie wystąpiły dla zadania

Jeśli okaże się, że żadna linia nie wymaga obsługi, zgłoszenie zadania jest kasowane.

Po wybraniu typu zadania przeglądane są bajty warunków wszystkich linie (począwszy od linii A+1, gdzie A jest poprzednio obsługiwaną linią). Podejmowana jest obsługa pierwszej linii, która jej wymaga, a wykonywana akcja zależy od tego, jakie zdarzenie nastąpiło w linii. Priorytetem jest zawartość bajtu warunku (od najwyższego priorytetu):

| Oznaczenie | Wartość | Opis |

|---|---|---|

| - | 00000001 | start zadania |

| WAODB | 00000010 | przesyłaj - zakończony odbiór |

| WANAD | 00000100 | przesyłaj - zakończone nadawanie |

| WAAWA | 00001000 | przesyłaj - awaria |

| WAOPR | 00010000 | przesyłaj - OPRQ |

| WAFWI | 00100000 | przesyłaj - winchester zakończył, XON dla monitorów |

| WATIM | 10000000 | przesyłaj - timeout (timer) |

Warunek WAFWI dla winchesterów oznacza zwolnienie kontrolera. Kontroler może w danej chwili obsługiwać tylko jeden dysk. Jeśli inna linia (inny winchester) chce transmitować dane, musi poczekać, aż obecnie transmitująca linia zwolni kontroler.

Odebranie zadania

- poszukaj w PZGLI zgłoszonego zadania o najwyższym priorytecie

- wpisz nr.zad do IDZAD

- wybierz linię, od której zaczniesz szukać (następna, bądź 0 jeśli pracowała ostatnia) i iteruj po wszystkich liniach

- jeśli dla żadnej linii nie znaleziono zgłoszenia -> zeruj zgłoszenia zadania dla wszystkich linii

- jeśli dla linii jest jakieś zgłoszenie -> startuj zadanie

- wyślij przerwanie liniowe

- ponownie uruchom manager zadań

Status linii

Polecenie liniowe "podaj status" zwraca status linii opisany strukturą STATL. Dokumentacja opisuje znaczenie tylko niektórych jej bitów, poniżej kompletny opis dwóch bajtów składających się na status. Numeracja bitów MERY-400 (0=MSB, 15=LSB). W słowie statusu jest jeszcze trzeci bajt, niedostępny dla programisty, opisujący status USART-a.

| Bit | Opis |

|---|---|

| 0 | 0 |

| 1 | Nadawanie ostatniego fragmentu |

| 2 | Nadawanie zawieszone przez XOFF |

| 3 | Zadanie zawieszone przez XOFF |

| 4 | - |

| 5 | - |

| 6 | Aktywna transmisja |

| 7 | Linia dołączona |

| 8 | OPRQ |

| 9 | Błąd parzystości |

| 10 | Odebrano znak kończący |

| 11 | Stop po CAN (protokół 5) |

| 12 | Odbiór w toku |

| 13 | Odbiór rozpoczęty |

| 14 | Nadawanie w toku |

| 15 | Nadawanie rozpoczęte |